# **TAS1020A** USB Streaming Controller

# Data Manual

December 2001

**Digital Audio Products**

SLES003A

# Contents

| Se | ection |           | Title                                              | Page |

|----|--------|-----------|----------------------------------------------------|------|

| 1  | Introc | luction . |                                                    | 1–1  |

|    | 1.1    | Feature   | s                                                  | 1–1  |

|    | 1.2    | Functior  | nal Block Diagram                                  | 1–3  |

|    | 1.3    | Termina   | Il Assignments—Normal Mode                         | 1–3  |

|    | 1.4    | Termina   | Il Assignments—External MCU Mode                   | 1–4  |

|    | 1.5    | Ordering  | g Information                                      | 1–4  |

|    | 1.6    | Termina   | Il Functions—Normal Mode                           | 1–5  |

|    | 1.7    | Termina   | Il Functions—External MCU Mode                     | 1–6  |

|    | 1.8    | Device (  | Operation Modes                                    | 1–7  |

|    | 1.9    | Termina   | I Assignments for Codec Port Interface Modes       | 1–7  |

| 2  | Desci  |           |                                                    |      |

|    | 2.1    | Archited  | ctural Overview                                    | 2–1  |

|    |        | 2.1.1     | Oscillator and PLL                                 | 2–1  |

|    |        | 2.1.2     | Clock Generator and Sequencer Logic                | 2–1  |

|    |        | 2.1.3     | Adaptive Clock Generator (ACG)                     | 2–1  |

|    |        | 2.1.4     | USB Transceiver                                    | 2–1  |

|    |        | 2.1.5     | USB Serial Interface Engine (SIE)                  | 2–1  |

|    |        | 2.1.6     | USB Buffer Manager (UBM)                           | 2–2  |

|    |        | 2.1.7     | USB Frame Timer                                    | 2–2  |

|    |        | 2.1.8     | USB Suspend and Resume Logic                       | 2–2  |

|    |        | 2.1.9     | MCU Core                                           | 2–2  |

|    |        | 2.1.10    | MCU Memory                                         | 2–2  |

|    |        | 2.1.11    | USB Endpoint Configuration Blocks and Buffer Space | 2–2  |

|    |        | 2.1.12    | DMA Controller                                     | 2–2  |

|    |        | 2.1.13    | Codec Port Interface                               | 2–3  |

|    |        | 2.1.14    | I <sup>2</sup> C Interface                         | 2–3  |

|    |        | 2.1.15    | General-Purpose IO Ports (GPIO)                    |      |

|    |        | 2.1.16    | Interrupt Logic                                    | 2–3  |

|    |        | 2.1.17    | Reset Logic                                        | 2–3  |

|    | 2.2    | Device (  | Operation                                          | 2–3  |

|    |        | 2.2.1     | Clock Generation                                   | 2–4  |

|    |        | 2.2.2     | Boot Process                                       | 2–4  |

|    |        | 2.2.3     | USB Enumeration                                    | 2–8  |

|    |        | 2.2.4     | TAS1020A USB Reset Logic                           | 2–9  |

|    |        | 2.2.5     | USB Suspend and Resume Modes                       | 2–10 |

|    |        | 2.2.6     | Adaptive Clock Generator (ACG)                     | 2–11 |

|    |        | 2.2.7     | USB Transfers                                      | 2–14 |

|    |        | 2.2.8     | Microcontroller Unit                               | 2–24 |

|   |        | 2.2.9     | External MCU Mode Operation                                                                    | 2–24 |

|---|--------|-----------|------------------------------------------------------------------------------------------------|------|

|   |        | 2.2.10    | Interrupt Logic                                                                                | 2–24 |

|   |        | 2.2.11    | General-Purpose I/O (GPIO) Ports                                                               | 2–29 |

|   |        | 2.2.12    | DMA Controller                                                                                 | 2–32 |

|   |        | 2.2.13    | Codec Port Interface                                                                           | 2–32 |

|   |        | 2.2.14    | I <sup>2</sup> C Interface                                                                     | 2–43 |

| 3 | Electr | rical Spe | cifications                                                                                    | 3–1  |

|   | 3.1    |           | e Maximum Ratings Over Operating                                                               |      |

|   |        | •         | ature Ranges                                                                                   |      |

|   | 3.2    |           | mended Operating Conditions                                                                    | 3–1  |

|   | 3.3    |           | al Characteristics Over Recommended                                                            | 3–1  |

|   | 3.4    | •         | Characteristics                                                                                | -    |

|   | 0.4    | 3.4.1     | Clock and Control Signals Over Recommended                                                     | 02   |

|   |        | 0.1.1     | Operating Conditions                                                                           | 3–2  |

|   |        | 3.4.2     | USB Signals When Sourced by TAS1020A Over                                                      |      |

|   |        |           | Recommended Operating Conditions                                                               | 3–2  |

|   |        | 3.4.3     | Codec Port Interface Signals (AC '97 Modes),                                                   |      |

|   |        |           | $T_A = 25^{\circ}C, DV_{DD} = 3.3 V, AV_{DD} = 3.3 V \dots$                                    | 3–3  |

|   |        | 3.4.4     | Codec Port Interface Signals (I <sup>2</sup> S Modes) Over<br>Recommended Operating Conditions | 3–4  |

|   |        | 3.4.5     | Codec Port Interface Signals (General-Purpose Mode)                                            | 3-4  |

|   |        | 3.4.5     | Over Recommended Operating Conditions                                                          | 3–4  |

|   |        | 3.4.6     | I <sup>2</sup> C Interface Signals Over Recommended                                            | 0.   |

|   |        |           | Operating Conditions                                                                           | 3–5  |

| 4 | Appli  | cation In | formation                                                                                      | 4–1  |

| Α | MCU    | Memory    | and Memory-Mapped Registers                                                                    | A–1  |

|   | A.1    | MCU M     | emory Space                                                                                    | A-1  |

|   | A.2    | Internal  | Data Memory                                                                                    | A-2  |

|   | A.3    | Externa   | I MCU Mode Memory Space                                                                        | A–3  |

|   | A.4    | USB En    | hdpoint Configuration Blocks and Data Buffer Space                                             | A-4  |

|   |        | A.4.1     | USB Endpoint Configuration Blocks                                                              | A-4  |

|   |        | A.4.2     | Data Buffer Space                                                                              | A-4  |

|   |        | A.4.3     | USB OUT Endpoint Configuration Bytes                                                           | A-9  |

|   |        | A.4.4     | USB IN Endpoint Configuration Bytes                                                            | A–12 |

|   |        | A.4.5     | USB Control Endpoint Setup Stage Data Packet Buffer                                            | A–15 |

|   | A.5    | Memory    | /-Mapped Registers                                                                             | A–16 |

|   |        | A.5.1     | USB Registers                                                                                  | A–18 |

|   |        | A.5.2     | DMA Registers                                                                                  | A–21 |

|   |        | A.5.3     | Adaptive Clock Generator Registers                                                             | A–25 |

|   |        | A.5.4     | Codec Port Interface Registers                                                                 | A–28 |

|   |        | A.5.5     | P3 Mask Register                                                                               | A-38 |

|   |        | A.5.6     | I <sup>2</sup> C Interface Registers                                                           | A-38 |

|   |        | A.5.7     | Miscellaneous Registers                                                                        | A–41 |

| В | Mech   | anical Da | ata                                                                                            | B–1  |

# List of Illustrations

| Figure Title                                                      | Page |

|-------------------------------------------------------------------|------|

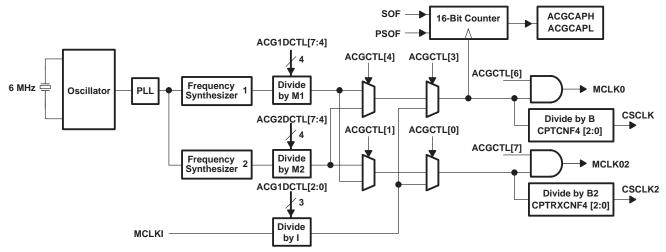

| 2–1 Adaptive Clock Generator                                      | 2–12 |

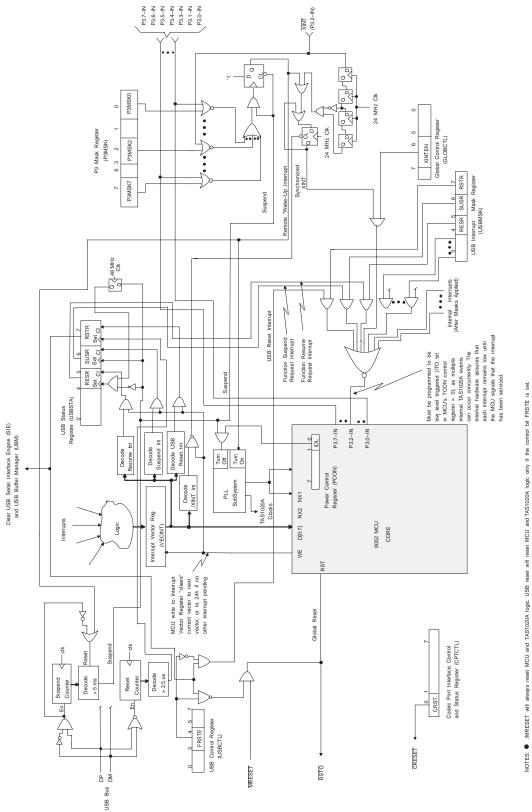

| 2-2 TAS1020A Interrupt, Reset, Suspend, and Resume Logic          | 2–25 |

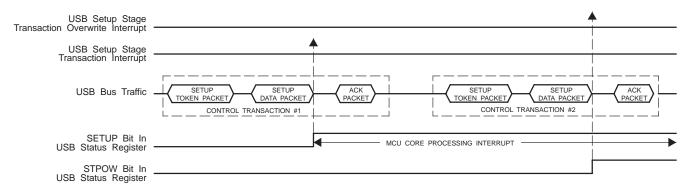

| 2–3 Activation of Setup Stage Transaction Overwrite Interrupt     | 2–27 |

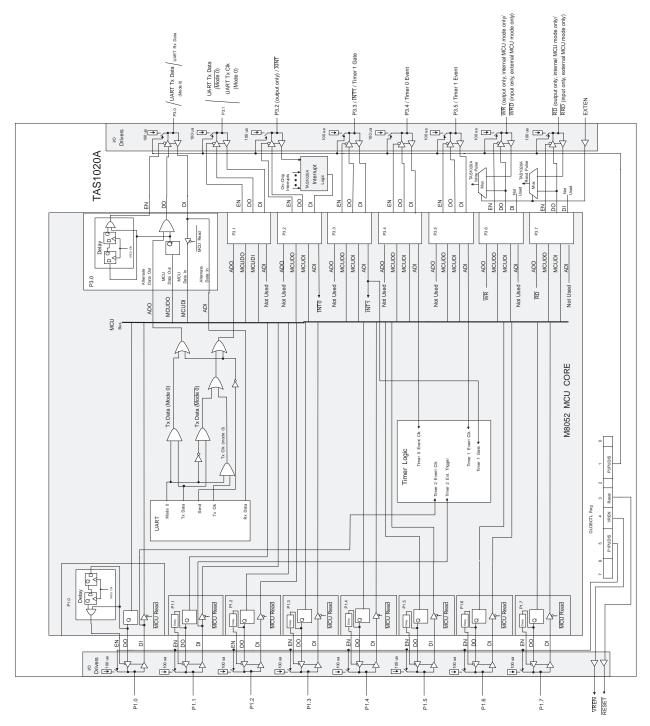

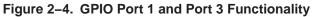

| 2–4 GPIO Port 1 and Port 3 Functionality                          | 2–30 |

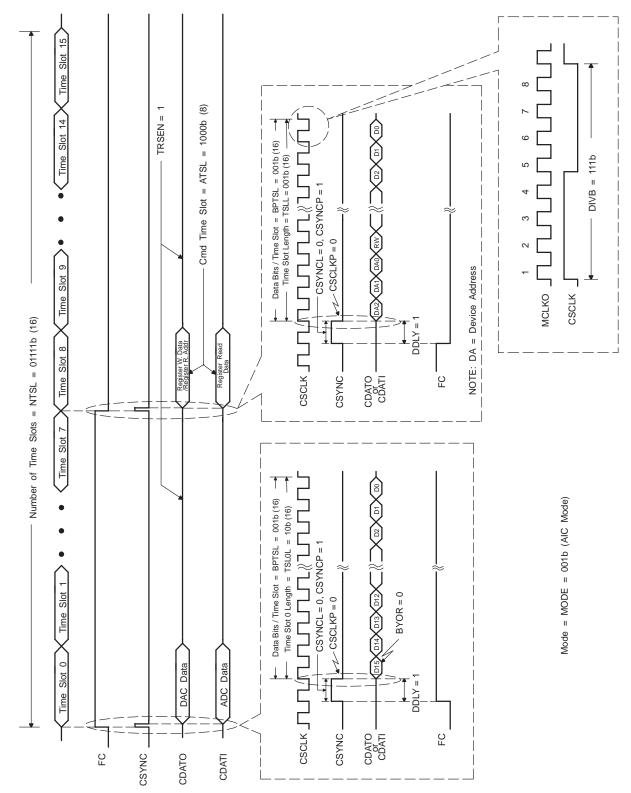

| 2–5 Codec Port Interface Parameters – AC '97 1.0                  | 2–35 |

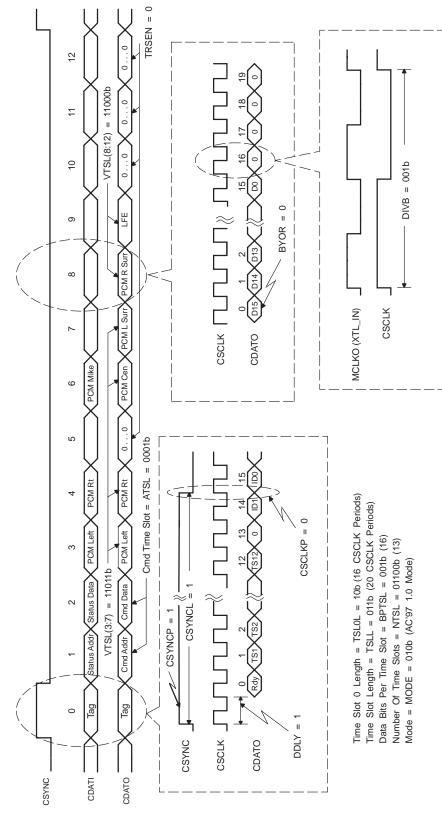

| 2–6 Codec Port Interface Parameters – AIC                         | 2–36 |

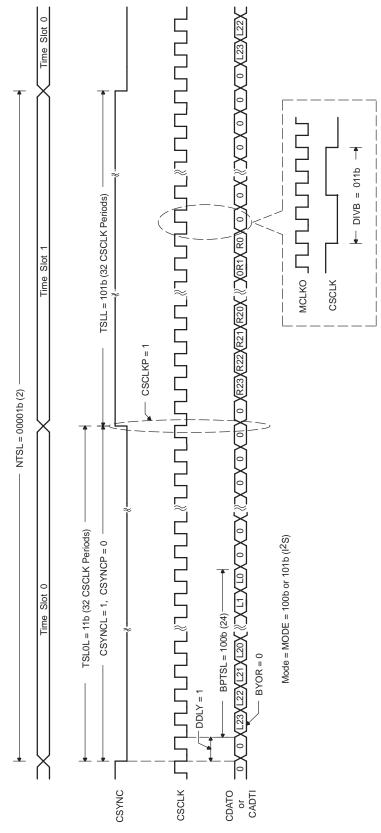

| 2–7 Codec Port Interface Parameters – I <sup>2</sup> S            | 2–38 |

| 2–8 Byte Reversal Example                                         | 2–39 |

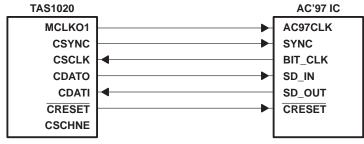

| 2–9 Connection of the TAS1020A to an AC '97 Codec                 | 2–40 |

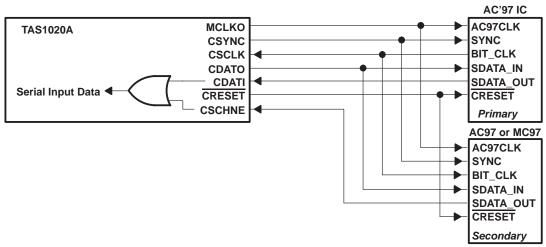

| 2-10 Connection of the TAS1020A to Multiple AC '97 Codecs         |      |

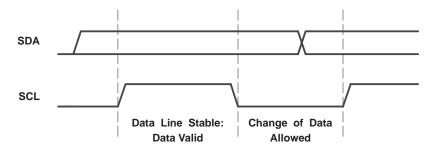

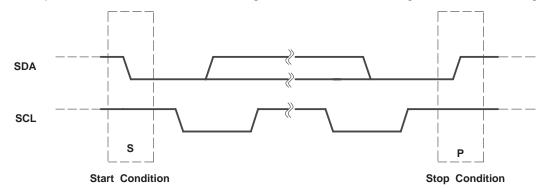

| 2–11 Bit Transfer on the I <sup>2</sup> C Bus                     |      |

| 2–12 I <sup>2</sup> C START and STOP Conditions                   | 2–44 |

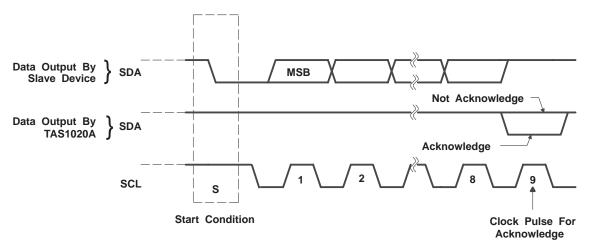

| 2–13 TAS1020A Acknowledge on the I <sup>2</sup> C Bus             | 2–45 |

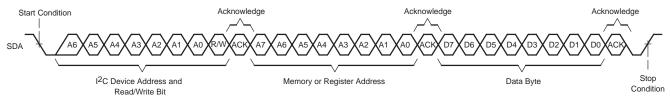

| 2–14 Single Byte Write Transfer                                   | 2–45 |

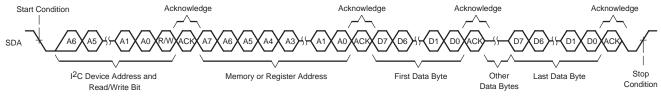

| 2–15 Multiple Byte Write Transfer                                 | 2–45 |

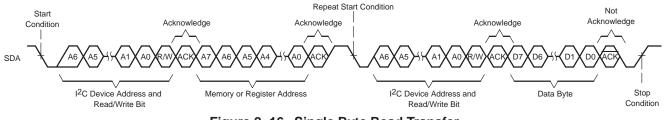

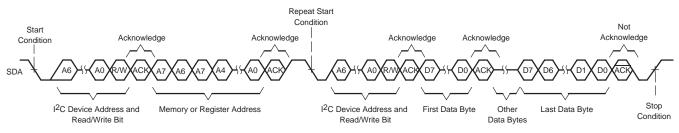

| 2–16 Single Byte Read Transfer                                    | 2–46 |

| 2–17 Multiple Byte Read Transfer                                  | 2–46 |

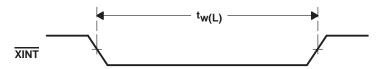

| 3–1 External Interrupt Timing Waveform                            | 3–2  |

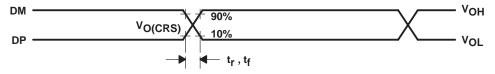

| 3–2 USB Differential Driver Timing Waveform                       | 3–2  |

| 3–3 BIT_CLK and SYNC Timing Waveforms                             | 3–3  |

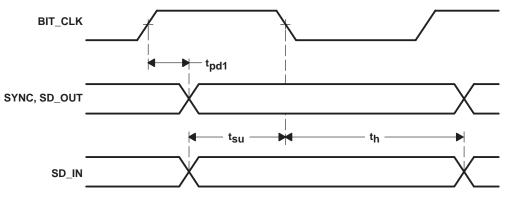

| 3–4 SYNC, SD_IN, and SD_OUT Timing Waveforms                      | 3–3  |

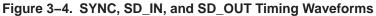

| 3–5 I <sup>2</sup> S Mode Timing Waveforms                        | 3–4  |

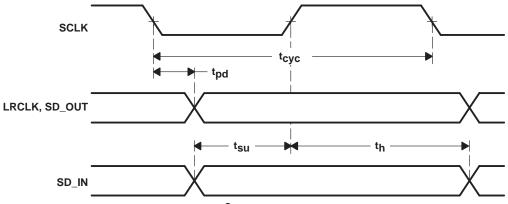

| 3–6 General-Purpose Mode Timing Waveforms                         | 3–4  |

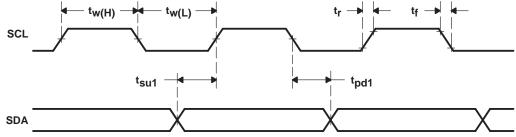

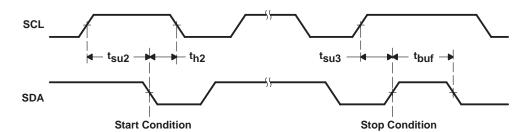

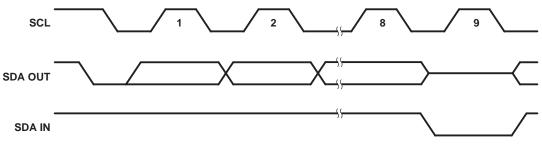

| 3–7 SCL and SDA Timing Waveforms                                  |      |

| 3–8 Start and Stop Conditions Timing Waveforms                    | 3–5  |

| 3–9 Acknowledge Timing Waveform                                   | 3–5  |

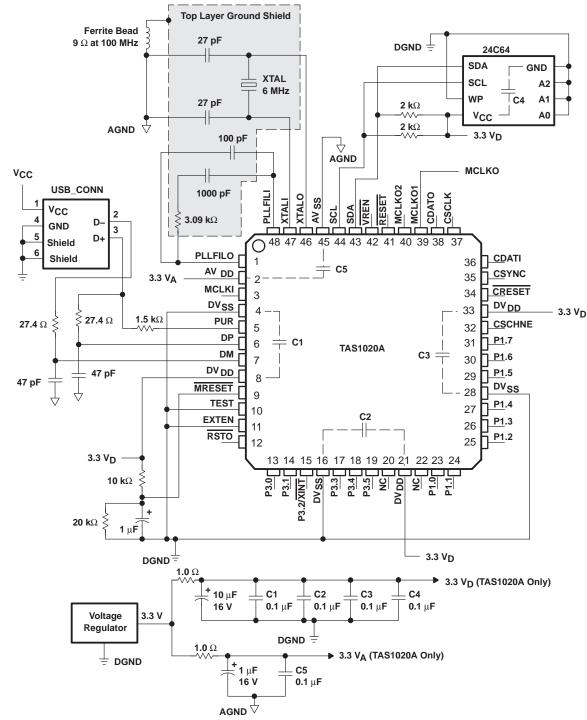

| 4–1 Typical TAS1020A Device Connections                           | 4–1  |

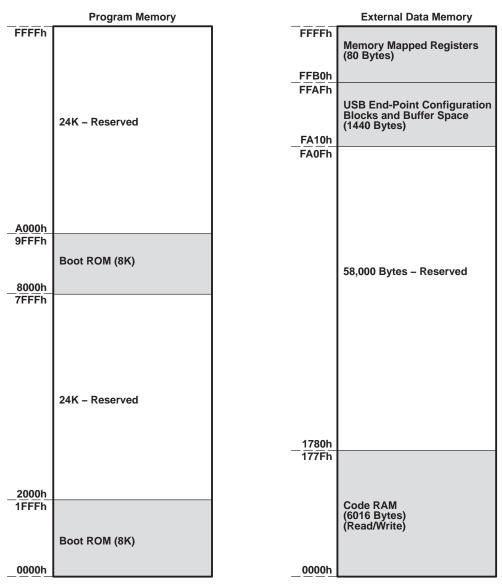

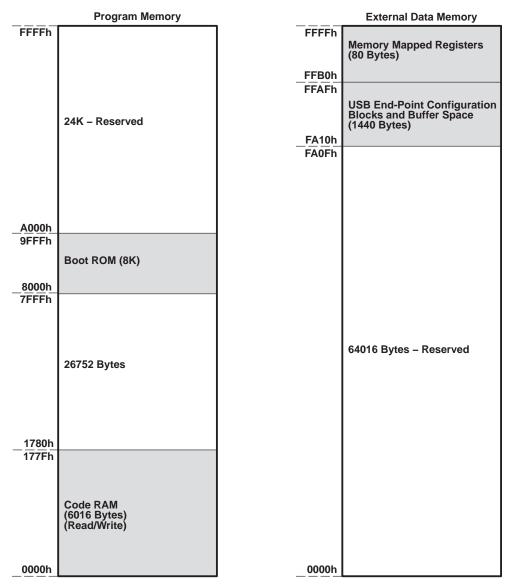

| A-1 Boot Loader Mode Memory Map                                   |      |

| A-2 Normal Operating Mode Memory Map                              |      |

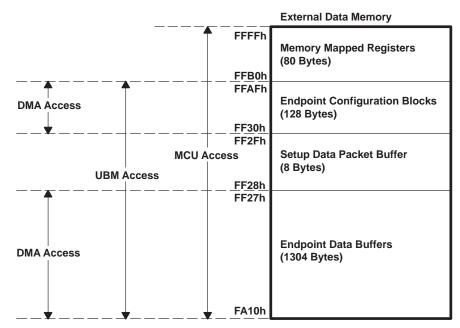

| A-3 USB Endpoint Configuration Blocks and Buffer Space Memory Map | A–5  |

# **List of Tables**

| Tabl | e Title                                                            | Page |

|------|--------------------------------------------------------------------|------|

| 2–1  | EEPROM Header                                                      | 2–6  |

| 2–2  | ACG Frequency Registers                                            | 2–13 |

| 2–3  | Terminal Assignments for Codec Port Interface General-Purpose Mode | 2–33 |

| 2–4  | Terminal Assignments for Codec Port Interface AC '97 1.0 Mode      | 2–39 |

| 2–5  | Terminal Assignments for Codec Port Interface AC '97 2.0 Mode      | 2–40 |

| 2–6  | Terminal Assignments for Codec Port Interface I2S Modes            | 2–41 |

| 2–7  | SLOT Assignments for Codec Port Interface I <sup>2</sup> S Mode 4  | 2–42 |

| 2–8  | SLOT Assignments for Codec Port Interface I <sup>2</sup> S Mode 5  | 2–42 |

| 2–9  | Terminal Assignments for Codec Port Interface AIC Mode             | 2–43 |

| A-1  | USB Endpoint Configuration Blocks Address Map                      | A-6  |

| A-2  | USB Control Endpoint Setup Data Packet Buffer Address Map          | A–15 |

| A-3  | Memory-Mapped Registers Address Map                                | A–16 |

# **1** Introduction

The TAS1020A integrated circuit (IC) is a universal serial bus (USB) peripheral interface device designed specifically for applications that require isochronous data streaming. Applications include digital speakers, which require the streaming of digital audio data between the host PC and the speaker system via the USB connection. The TAS1020A device is fully compatible with the USB Specification Version 1.1 and the USB Audio Class Specification.

The TAS1020A uses a standard 8052 microcontroller unit (MCU) core with on-chip memory. The MCU memory includes 8K bytes of program memory ROM that contains a boot loader program. At initialization, the boot loader program downloads the application program code to a 6,016-byte RAM from either the host PC or a nonvolatile memory on the printed-circuit board (PCB). The MCU handles all USB control, interrupt and bulk endpoint transactions. DMA channels are provided to handle isochronous endpoint transactions.

The USB interface includes an integrated transceiver that supports 12 Mb/s (full speed) data transfers. In addition to the USB control endpoint, support is provided for up to seven IN endpoints and seven OUT endpoints. The USB endpoints are fully configurable by the MCU application code using a set of endpoint configuration blocks that reside in on-chip RAM. All USB data transfer types are supported.

The TAS1020A device also includes a codec port interface (C-Port) that can be configured to support several industry standard serial interface protocols. These protocols include the audio codec (AC) '97 Revision 1.X, the audio codec (AC) '97 Revision 2.X and several inter-IC sound (I<sup>2</sup>S) modes.

A direct memory access (DMA) controller with two channels is provided for streaming the USB isochronous data packets to/from the codec port interface. Each DMA channel can support one USB isochronous endpoint.

An on-chip phase lock loop (PLL) and adaptive clock generator (ACG) provide support for the USB synchronization modes, which include asynchronous, synchronous and adaptive.

Other on-chip MCU peripherals include an inter-IC control (I<sup>2</sup>C) serial interface, and two 8-bit general-purpose input/output (GPIO) ports.

The TAS1020A device is implemented in a 3.3-V 0.25  $\mu m$  CMOS technology.

#### 1.1 Features

- Universal Serial Bus (USB)

- USB specification version 1.1 compatible

- USB audio class specification 1.0 compatible

- Integrated USB transceiver

- Supports 12 Mb/s data rate (full speed)

- Supports suspend/resume and remote wake-up

- Supports control, interrupt, bulk, and isochronous data transfer types

- Supports up to a total of seven IN endpoints and seven OUT endpoints in addition to the control endpoint

- Data transfer type, data buffer size, single or double buffering is programmable for each endpoint

- On-chip adaptive clock generator (ACG) supports asynchronous, synchronous and adaptive synchronization modes for isochronous endpoints

- To support synchronization for streaming USB audio data, the ACG can be used to generate the master clock for the codec

#### • Micro-Controller Unit (MCU)

- Standard 8052 8-bit core

- 8K bytes of program memory ROM that contains a boot loader program and a library of commonly used USB functions

- 6016 bytes of program memory RAM which is loaded by the boot loader program

- 256 bytes of internal data memory RAM

- Two GPIO ports

- MCU handles all USB control, interrupt, and bulk endpoint transfers

- DMA Controller

- Two DMA channels to support streaming USB audio data to/from the codec port interface

- Each channel can support a single USB isochronous endpoint

- In the I<sup>2</sup>S mode the device can support DAC/ADCs at different sampling frequencies

- A circular programmable FIFO used for isochronous audio data streaming

- Codec Port Interface

- Configurable to support AC'97 1.X, AC'97 2.X, AIC or I<sup>2</sup>S serial interface formats

- I<sup>2</sup>S modes can support a combination of one DAC and/or two ADCs

- Can be configured as a general-purpose serial interface

- Can support bulk data transfer using DMA for higher throughput

#### • I<sup>2</sup>C Interface

- Master only interface

- Does not support a multimaster bus environment

- Programmable to 100 kb/s or 400 kb/s data transfer speeds

- Supports wait states to accommodate slow slaves

- General Characteristics

- High performance 48-pin TQFP Package

- On-chip phase-locked loop (PLL) with internal oscillator is used to generate internal clocks from a 6 MHz crystal input

- Reset output available which is asserted for both system and USB reset

- External MCU mode supports application firmware development

- 8K ROM with boot loader program and commonly used USB functions library

- 3.3 V core and I/O buffers

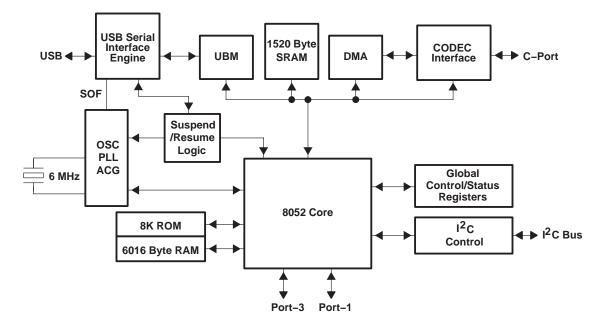

## 1.2 Functional Block Diagram

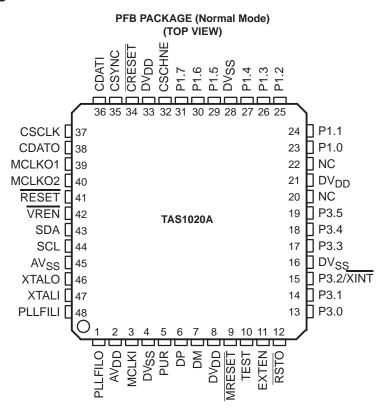

## 1.3 Terminal Assignments—Normal Mode

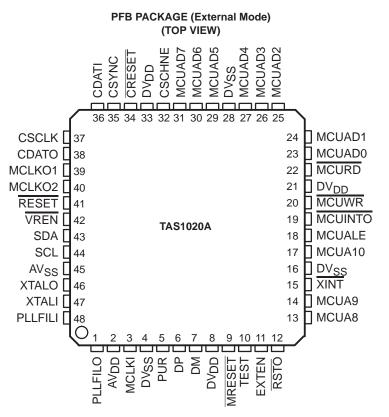

#### 1.4 Terminal Assignments—External MCU Mode

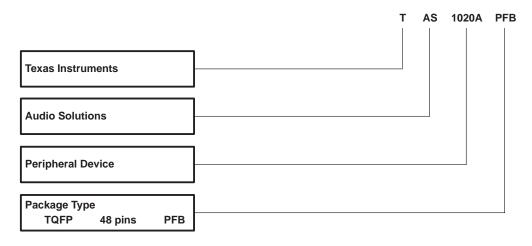

# 1.5 Ordering Information

# 1.6 Terminal Functions—Normal Mode

| TERMINAL         |             |                                         |     |                                                                                                                                                                                                                                                                                 |  |  |  |

|------------------|-------------|-----------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME             | PIN<br>TYPE | NO.                                     | I/O | DESCRIPTION                                                                                                                                                                                                                                                                     |  |  |  |

| AV <sub>DD</sub> | Power       | 2                                       |     | 3.3-V analog supply voltage                                                                                                                                                                                                                                                     |  |  |  |

| AVSS             | Power       | 45                                      |     | Analog ground                                                                                                                                                                                                                                                                   |  |  |  |

| CSCLK            | CMOS        | 37                                      | I/O | Codec port interface serial clock: CSCLK is the serial clock for the codec port interface used to clock the CSYNC, CDATO, CDATI, CRESET, AND CSCHNE signals.                                                                                                                    |  |  |  |

| CSYNC            | CMOS        | 35                                      | I/O | Codec port interface frame sync: CSYNC is the frame synchronization signal for the codec port interface.                                                                                                                                                                        |  |  |  |

| CDATO            | CMOS        | 38                                      | I/O | Codec port interface serial data out                                                                                                                                                                                                                                            |  |  |  |

| CDATI            | CMOS        | 36                                      | I/O | Codec port interface serial data in                                                                                                                                                                                                                                             |  |  |  |

| CRESET           | CMOS        | 34                                      | I/O | Codec port interface reset output                                                                                                                                                                                                                                               |  |  |  |

| CSCHNE           | CMOS        | 32                                      | I/O | Codec port interface secondary channel enable                                                                                                                                                                                                                                   |  |  |  |

| DP               | CMOS        | 6                                       | I/O | USB differential pair data signal plus. DP is the positive signal of the bidirectional USB differential pair used to connect the TAS1020A device to the universal serial bus.                                                                                                   |  |  |  |

| DM               | CMOS        | 7                                       | I/O | USB differential pair data signal minus. DM is the negative signal of the bidirectional USB differential pair used to connect the TAS1020A device to the universal serial bus.                                                                                                  |  |  |  |

| DVDD             | Power       | 8, 21, 33                               |     | 3.3-V digital supply voltage                                                                                                                                                                                                                                                    |  |  |  |

| DVSS             | Power       | 4, 16, 28                               |     | Digital ground                                                                                                                                                                                                                                                                  |  |  |  |

| EXTEN            | CMOS        | 11                                      | Ι   | External MCU mode enable: Input used to enable the device for the external MCU mode                                                                                                                                                                                             |  |  |  |

| MCLKI            | CMOS        | 3                                       | I   | Master clock input. An input that can be used as the master clock for the codec port interface or the source for MCLKO2.                                                                                                                                                        |  |  |  |

| MCLKO1           | CMOS        | 39                                      | 0   | Master clock output 1: The output of the ACG that can be used as the master clock for the codec printerface and the codec.                                                                                                                                                      |  |  |  |

| MCLKO2           | CMOS        | 40                                      | 0   | Master clock output 2: An output that can be used as the master clock for the codec port interface a the codec used in I <sup>2</sup> S modes for receive. This clock signal can also be used as a miscellaneo clock.                                                           |  |  |  |

| MRESET           | CMOS        | 9                                       | Ι   | Master reset: An active low asynchronous reset for the device that resets all logic to the default state                                                                                                                                                                        |  |  |  |

| NC               |             | 20,22                                   |     | Not used                                                                                                                                                                                                                                                                        |  |  |  |

| P1.[0:7]         | CMOS        | 23, 24,<br>25, 26,<br>27, 29,<br>30, 31 | I/O | General-purpose I/O port [bits 0 through 1]: A bidirectional 8-bit I/O port with an internal 100 $\mu A$ active pullup                                                                                                                                                          |  |  |  |

| P3.[0:6]         | CMOS        | 13, 14,<br>15, 17,<br>18, 19            | I/O | General-purpose I/O port [bits 0 through 1]: A bidirectional I/O port with an internal 100 $\mu A$ active pullup                                                                                                                                                                |  |  |  |

| PLLFILI          | CMOS        | 48                                      | I   | PLL loop filter input: Input to on-chip PLL from external filter components                                                                                                                                                                                                     |  |  |  |

| PLLFILO          | CMOS        | 1                                       | 0   | PLL loop filter output: Output from on-chip PLL to external filter components                                                                                                                                                                                                   |  |  |  |

| PUR              | CMOS        | 5                                       | 0   | USB data signal plus pullup resistor connect. PUR is used to connect the pullup resistor on the DP signal from a high-impedance state to 3.3 V. When the DP signal is connected to 3.3-V the host PC detects the connection of the TAS1020A device to the universal serial bus. |  |  |  |

| RESET            | CMOS        | 41                                      | 0   | General-purpose active-low output which is memory mapped                                                                                                                                                                                                                        |  |  |  |

| RSTO             | CMOS        | 12                                      | 0   | Reset output: An output that is active while the master reset input or the USB reset is active                                                                                                                                                                                  |  |  |  |

| SCL              | CMOS        | 44                                      | 0   | I <sup>2</sup> C interface serial clock                                                                                                                                                                                                                                         |  |  |  |

| SDA              | CMOS        | 43                                      | I/O | I <sup>2</sup> C interface serial data                                                                                                                                                                                                                                          |  |  |  |

| TEST             | CMOS        | 10                                      | I   | Test mode enable: Factory test mode                                                                                                                                                                                                                                             |  |  |  |

| VREN             | CMOS        | 42                                      | 0   | General-purpose active-low output which is memory mapped                                                                                                                                                                                                                        |  |  |  |

| XINT             | CMOS        | 15                                      | Ι   | External interrupt: An active low input used by external circuitry to interrupt the on-chip 8052 MCU                                                                                                                                                                            |  |  |  |

| XTALI            | CMOS        | 47                                      | I   | Crystal input: Input to the on-chip oscillator from an external 6-MHz crystal                                                                                                                                                                                                   |  |  |  |

| XTALO            | CMOS        | 46                                      | 0   | Crystal Output: Output from the on-chip oscillator to an external 6-MHz crystal                                                                                                                                                                                                 |  |  |  |

# 1.7 Terminal Functions—External MCU Mode

| TERMINAL             |       |                                      |             |                                                                                                                                                                                                                                                                                              |  |  |  |

|----------------------|-------|--------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME PIN<br>TYPE NO. |       | 1/0                                  | DESCRIPTION |                                                                                                                                                                                                                                                                                              |  |  |  |

| AVDD                 | Power | 2                                    | -           | 3.3-V Analog supply voltage                                                                                                                                                                                                                                                                  |  |  |  |

| AVSS                 | Power | 45                                   | -           | Analog ground                                                                                                                                                                                                                                                                                |  |  |  |

| CSCLK                | CMOS  | 37                                   | I/O         | Codec port interface serial clock: CSCLK is the serial clock for the codec port interface used to clock the CSYNC, CDATO, CDATI, CRESET AND CSCHNE signals.                                                                                                                                  |  |  |  |

| CSYNC                | CMOS  | 35                                   | I/O         | Codec port interface frame sync: CSYNC is the frame synchronization signal for the codec port interface.                                                                                                                                                                                     |  |  |  |

| CDATO                | CMOS  | 38                                   | I/O         | Codec port interface serial data output                                                                                                                                                                                                                                                      |  |  |  |

| CDATI                | CMOS  | 36                                   | I/O         | Codec port interface serial data input                                                                                                                                                                                                                                                       |  |  |  |

| CRESET               | CMOS  | 34                                   | I/O         | Codec port interface reset output                                                                                                                                                                                                                                                            |  |  |  |

| CSCHNE               | CMOS  | 32                                   | I/O         | Codec port interface secondary channel enable                                                                                                                                                                                                                                                |  |  |  |

| DP                   | CMOS  | 6                                    | I/O         | USB differential pair data signal plus: DP is the positive signal of the bidirectional USB differential pair used to connect the TAS1020A device to the universal serial bus.                                                                                                                |  |  |  |

| DM                   | CMOS  | 7                                    | I/O         | USB differential pair data signal minus. DM is the negative signal of the bidirectional USB differen-<br>tial pair used to connect the TAS1020A device to the universal serial bus.                                                                                                          |  |  |  |

| DVDD                 | Power | 8, 21, 33                            | -           | 3.3-V Digital supply voltage                                                                                                                                                                                                                                                                 |  |  |  |

| DVSS                 | Power | 4, 16, 28                            | -           | Digital ground                                                                                                                                                                                                                                                                               |  |  |  |

| EXTEN                | CMOS  | 11                                   | I           | External MCU mode enable: Input used to enable the device for the external MCU mode. This sig-<br>nal uses a 3.3 V TTL/LVCMOS input buffer.                                                                                                                                                  |  |  |  |

| MCLKI                | CMOS  | 3                                    | I           | Master clock input: An input that can be used as the master clock for the codec port interface or the source for MCLKO2.                                                                                                                                                                     |  |  |  |

| MCLKO1               | CMOS  | 39                                   | 0           | Master clock output 1: The output of the ACG that can be used as the master clock for the codec port interface and the codec.                                                                                                                                                                |  |  |  |

| MCLKO2               | CMOS  | 40                                   | 0           | Master clock output 2: An output that can be used as the master clock for the codec port interface and the codec. This clock signal can also be used as a miscellaneous clock.                                                                                                               |  |  |  |

| MRESET               | CMOS  | 9                                    | I           | Master reset: An active low asynchronous reset for the device that resets all logic to the default state.                                                                                                                                                                                    |  |  |  |

| MCUAD<br>[0:7]       | CMOS  | 23, 24, 25,<br>26, 27, 29,<br>30, 31 | I/O         | MCU multiplexed address/data: Multiplexed address bits[0:7]/data bits[0:7] for external MCU access to the TAS1020A external data memory space.                                                                                                                                               |  |  |  |

| MCUA<br>[8:10]       | CMOS  | 13, 14, 17                           | I/O         | MCU address bus: Multiplexed address bus bits[8:10] for external MCU access to the TAS1020A external data memory space.                                                                                                                                                                      |  |  |  |

| MCUALE               | CMOS  | 18                                   | I           | MCU address latch enable: Address latch enable for external MCU access to the TAS1020A exter-<br>nal data memory space.                                                                                                                                                                      |  |  |  |

| MCUINTO              | CMOS  | 19                                   | 0           | MCU interrupt output: Interrupt output to be used for external MCU INTO input signal. All internal TAS1020A interrupt sources are read together to generate this output signal.                                                                                                              |  |  |  |

| MCUWR                | CMOS  | 20                                   | I           | MCU write strobe: Write strobe for external MCU write access to the TAS1020A external data memory space.                                                                                                                                                                                     |  |  |  |

| MCURD                | CMOS  | 22                                   | I           | MCU read strobe: Read strobe for external MCU read access to the TAS1020A external data memory space.                                                                                                                                                                                        |  |  |  |

| PLLFILI              | CMOS  | 48                                   | I           | PLL loop filter input: Input to on-chip PLL from external filter components.                                                                                                                                                                                                                 |  |  |  |

| PLLFILO              | CMOS  | 1                                    | 0           | PLL loop filter output: Output to on-chip PLL from external filter components.                                                                                                                                                                                                               |  |  |  |

| PUR                  | CMOS  | 5                                    | 0           | USB data signal plus pullup resistor connect. PUR is used to connect the pullup resistor on the DI signal to 3.3V from a high-impedance state. When the DP signal is connected in a 3.3-V state, th host PC should detect the connection of the TAS1020A device to the universal serial bus. |  |  |  |

| RESET                | CMOS  | 41                                   | 0           | General-purpose active-low output which is memory mapped                                                                                                                                                                                                                                     |  |  |  |

| RSTO                 | CMOS  | 12                                   | 0           | Reset output: An output that is active while the master reset input or the USB reset is active.                                                                                                                                                                                              |  |  |  |

| SCL                  | CMOS  | 44                                   | 0           | I <sup>2</sup> C interface serial clock                                                                                                                                                                                                                                                      |  |  |  |

| SDA                  | CMOS  | 43                                   | I/O         | I <sup>2</sup> C interface serial data input/output                                                                                                                                                                                                                                          |  |  |  |

| TEST                 | CMOS  | 10                                   | I           | Test mode enable: Factory text mode                                                                                                                                                                                                                                                          |  |  |  |

| -     | FERMINAL    | -   |     |                                                                                                       |

|-------|-------------|-----|-----|-------------------------------------------------------------------------------------------------------|

| NAME  | PIN<br>TYPE | NO. | I/O | DESCRIPTION                                                                                           |

| VREN  | CMOS        | 42  | 0   | General-purpose active-low output which is memory mapped.                                             |

| XINT  | CMOS        | 15  | Ι   | External interrupt: An active low input used by external circuitry to interrupt the on-chip 8052 MCU. |

| XTALI | CMOS        | 47  | Ι   | Crystal input: Input to the on-chip oscillator from an external 6-MHz crystal.                        |

| XTALO | CMOS        | 46  | 0   | Crystal output: Output from the on-chip oscillator to an external 6-MHz crystal.                      |

# 1.7 Terminal Functions—External MCU Mode (Continued)

# 1.8 Device Operation Modes

The EXTEN and TEST pins define the mode that the TAS1020A is in after reset.

| MODE                       | EXTEN | TEST |

|----------------------------|-------|------|

| Normal mode – internal MCU | 0     | 0    |

| External MCU mode          | 1     | 0    |

| Factory test               | 0     | 1    |

| Factory test               | 1     | 1    |

## 1.9 Terminal Assignments for Codec Port Interface Modes

The codec port interface has five modes of operation that support AC97, I<sup>2</sup>S, and AIC codecs. There is also a general-purpose mode that is not specific to a serial interface. The mode is programmed by writing to the mode select field of the codec port interface configuration register 1 (CPTCNF1). The codec port interface terminals CSYNC, CSCLK, CDATO, CDATI, CRESET, and CSCHNE take on functionality appropriate to the mode programmed as shown in the following table.

| TERMINAL |        | GP     |     | AIC   |   | AC '97 v1.X |   | AC '97 v2.X |   | l <sup>2</sup> S |   | l <sup>2</sup> S |   |

|----------|--------|--------|-----|-------|---|-------------|---|-------------|---|------------------|---|------------------|---|

| NO.      | NAME   | Mode 0 | )   | Mode  | 1 | Mode        | 2 | Mode        | 3 | Mode             | 4 | Mode             | 5 |

| 35       | CSYNC  | CSYNC  | I/O | FS    | 0 | SYNC        | 0 | SYNC        | 0 | LRCK             | 0 | LRCK1            | 0 |

| 37       | CSCLK  | CSCLK  | I/O | SCLK  | 0 | BIT_CLK     | I | BIT_CLK     | Ι | SCLK             | 0 | SCLK1            | 0 |

| 38       | CDATO  | CDATO  | 0   | DOUT  | 0 | SD_OUT      | 0 | SD_OUT      | 0 | SDOUT1           | 0 | SDOUT1           | 0 |

| 36       | CDATI  | CDATI  | Ι   | DIN   | Ι | SD_IN       | Ι | SD_IN1      | Ι | SDIN1            | Ι | SDIN2            | Ι |

| 34       | CRESET | CRESET | 0   | RESET | 0 | RESET       | 0 | RESET       | 0 | CRESET           | 0 | SCLK2            | 0 |

| 32       | CSCHNE | NC     | 0   | FC    | 0 | NC          | 0 | SD_IN2      | Ι | SDIN2            | I | LRCK2            | 0 |

NOTES: 1. Signal names and I/O direction are with respect to the TAS1020A device. The signal names used for the TAS1020A terminals for the various codec port interface modes reflect the nomenclature used by the codec devices.

2. NC indicates no connection for the terminal in a particular mode. The TAS1020A device drives the signal as an output for these cases.

3. The CSYNC and CSCLK signals can be programmed as either an input or an output in the general-purpose mode.

# 2 Description

# 2.1 Architectural Overview

## 2.1.1 Oscillator and PLL

Using an external 6-MHz crystal, the TAS1020A derives the fundamental 48-MHz internal clock signal using an on-chip oscillator and PLL. Using the PLL output, the other required clock signals are generated by the clock generator and adaptive clock generator.

# 2.1.2 Clock Generator and Sequencer Logic

Utilizing the 48-MHz output from the PLL, the clock generator logic generates all internal clock signals, except for the codec port interface master clock (MCLK) and serial clock (CSCLK) signals. The TAS1020A internal clocks include the 48-MHz clock, a 24-MHz clock, and a 12-MHz clock. A 12 MHz USB clock is also generated. The USB clock is the same as the internal 12-MHz clock when the TAS1020A is transmitting data, but is derived from the data when the TAS1020A is receiving data. To derive the USB clock when receiving USB data, the TAS1020A utilizes an internal digital PLL (DPLL) driven from the 48-MHz clock.

The sequencer logic controls the access to the SRAM used for the USB endpoint configuration blocks and the USB endpoint buffer space. The SRAM can be accessed by the MCU, the USB buffer manager (UBM), or the DMA channels. The sequencer controls the access to the memory using a round-robin fixed priority arbitration scheme. This means that the sequencer logic generates grant signals for the MCU, UBM, and DMA channels at a predetermined fixed frequency.

# 2.1.3 Adaptive Clock Generator (ACG)

The adaptive clock generator is used to generate a master clock output signal (MCLKO) to be used by the codec port interface and the codec device. To synchronize data sent to or received from the codec to the USB frame rate, the MCLKO signal generated by the adaptive clock generator must be used. The synchronization of the MCLKO signal to the USB frame rate is achieved by the ACG, which, in turn, is controlled by a soft PLL, implemented in the MCU. One of the tasks performed by the ACG is to maintain count of the number of MCLKO clocks between USB Start of Frame (SOF) events. This count is monitored by the soft PLL in the MCU. Based on this count, the soft PLL outputs corrections to the ACG to adjust MCLKO to obtain the correct number of MCLKO clocks between USB SOF events.

MCLKI, the master clock input, can also be selected to source the clocks used by the codec port interface. When MCLKI is selected, it is used to derive the TAS1020A-sourced versions of the clocks CSCLK and CSYNC. In this scenario, the codec device would also use the same master clock signal (MCLKI).

# 2.1.4 USB Transceiver

The TAS1020A provides an integrated transceiver for the USB port. The transceiver includes a differential output driver, a differential input receiver, and two single ended input buffers. The transceiver connects to the USB DP and DM signal terminals.

# 2.1.5 USB Serial Interface Engine (SIE)

The serial interface engine logic manages the USB packet protocol for packets being received and transmitted by the TAS1020A. For packets being received, the SIE decodes the packet identifier field (PID) to determine the type of packet being received and to ensure the PID is valid. The SIE then calculates the cycle redundancy check (CRC) of the received token and data packets and compares the value to the CRC contained in the packet to verify that the packet was not corrupted during transmission. For transmitted token and data packets, the SIE generates the CRC that is transmitted with the packet. The SIE also generates the synchronization field (SYNC) and the correct PID for all transmitted packets. Another major function of the SIE is the serial-to-parallel conversion of received data packets and the parallel-to-serial conversion of transmitted data packets.

# 2.1.6 USB Buffer Manager (UBM)

The USB buffer manager provides the control logic that interfaces the SIE to the USB endpoint buffers. One of the major functions of the UBM is to decode the USB function address to determine if the host PC is addressing the TAS1020A device USB peripheral function. In addition, the endpoint address field and direction signal are decoded to determine which particular USB endpoint is being addressed. Based on the direction of the USB transaction and the endpoint number, the UBM will either write or read the data packet to or from the appropriate USB endpoint data buffer.

# 2.1.7 USB Frame Timer

The USB frame timer logic receives the start of frame (SOF) packet from the host PC each USB frame. Each frame, the logic stores the 11-bit frame number value from the SOF packet in a register and asserts the internal SOF signal. The frame number register can be read by the MCU and the value can be used as a time stamp. For USB frames in which the SOF packet is corrupted or not received, the frame timer logic will generate a pseudo start of frame (PSOF) signal and increment the frame number register.

# 2.1.8 USB Suspend and Resume Logic

The USB suspend and resume logic detects suspend and resume conditions on the USB. This logic also provides the internal signals used to control the TAS1020A device when these conditions occur. The capability to resume operation from a suspend condition with a locally generated remote wake-up event is also provided.

# 2.1.9 MCU Core

The TAS1020A uses an 8-bit microcontroller core that is based on the industry standard 8052. The MCU is software compatible with the 8052, 8032, 80C52, 80C53, and 87C52 MCUs. The 8052 MCU is the processing core of the TAS1020A and handles all USB control, interrupt and bulk endpoint transfers. Bulk out end-point transfers can also be handled by one of the two DMA channels.

# 2.1.10 MCU Memory

In accordance with the industry standard 8052, the TAS1020A MCU memory is organized into program memory, external data memory and internal data memory. A boot ROM program is used to download the application code to a 6K byte RAM that is mapped to the program memory space. The external data memory includes the USB endpoint configuration blocks, USB data buffers, and memory mapped registers. The total external data memory space available is 1.5K bytes. A total of 256 bytes are provided for the internal data memory.

# 2.1.11 USB Endpoint Configuration Blocks and Buffer Space

The USB endpoint configuration blocks are used by the MCU to configure and operate the required USB endpoints for a particular application. In addition to the control end-point, the TAS1020A supports a total of seven IN endpoints and seven OUT endpoints. A set of six bytes is provided for each endpoint to specify the endpoint type, buffer address, buffer size, and data packet byte count.

The USB endpoint buffer configuration blocks and buffer space provided totals 1440 bytes. The buffer space to be used by a particular endpoint is fully configurable by the MCU for a particular application. Therefore, the MCU can configure each buffer based on the total number of endpoints to be used, the maximum packet size to be used for each endpoint, and the selection of single or double buffering.

# 2.1.12 DMA Controller

Two DMA channels are provided to support the streaming of data for USB isochronous IN endpoints, isochronous OUT endpoints, and bulk OUT endpoints. Each DMA channel can support one USB isochronous IN endpoint, or one isochronous OUT endpoint, or one bulk OUT endpoint. The DMA channels are used to stream data between the USB

endpoint data buffers and the codec port interface. The USB endpoint number and direction can be programmed for each DMA channel. Also, the codec port interface time slots to be serviced by each DMA channel can be programmed.

#### 2.1.13 Codec Port Interface

The TAS1020A provides a configurable full duplex bidirectional serial interface that can be used to connect to a codec or other external device types for streaming USB isochronous data. The interface can be configured to support several different industry standard protocols, including AC '97 1.X, AC '97 2.X, AIC, and I<sup>2</sup>S. The TAS1020A also has a general-purpose mode to support other protocols.

# 2.1.14 I<sup>2</sup>C Interface

The I<sup>2</sup>C interface logic provides a two-wire serial interface that the 8052 MCU can use to access other ICs. The TAS1020A is an I<sup>2</sup>C master device only and supports single byte or multiple byte read and write operations. The interface can be programmed to operate at either 100 kbps or 400 kbps. In addition, the protocol supports 8-bit or 16-bit addressing for accessing the I<sup>2</sup>C slave device memory locations. The TAS1020A supports I<sup>2</sup>C wait states. This means slaves can assert wait state on the I<sup>2</sup>C bus by pulling the SCL line low.

## 2.1.15 General-Purpose IO Ports (GPIO)

The TAS1020A provides two general-purpose IO ports that are controlled by the internal 8052 MCU. The two ports are port 1 and port 3. Port 1 provides true GPIO capability. Each bit of port 1 can be independently used as either an input or output, and consists of an output buffer, an input buffer, and a pullup resistor. Some of the bits of port 3 also provide true GPIO capability, but, in addition, some of the bits of port 3 also provide alternate input and output uses. An example of this is P3.2, which is used as the external interrupt (XINT) input to the TAS1020A. A detailed description of the alternate uses of some of the port 3 bits is presented in Section 2.2.11.

The pullup resistors for port 1 and port 3 can be disabled by bits P1PUDIS and P3PUDIS respectively in the on-chip register GLOBCTL. In addition, any port 3 pin can be used to wake up the host PC from a low-power suspend mode.

#### 2.1.16 Interrupt Logic

The interrupt logic monitors the various conditions that can cause an interrupt and asserts the interrupt 0 (INTO) input on the 8052 MCU core accordingly. All of the TAS1020A internal interrupt sources and the external interrupt (XINT) input are ORed together to generate the INTO signal. An interrupt vector register is used by the MCU to identify the interrupt source.

# 2.1.17 Reset Logic

An external master reset (MRESET) input signal that is asynchronous to the internal clocks can be used to reset the TAS1020A logic. In addition to this master reset, the TAS1020A logic can also be reset by a USB reset from the host PC if bit FRSTE in the on-chip register USBCTL is set to 1. The TAS1020A also provides a reset output (RSTO) signal that can be used by external devices. This signal is asserted when either a master reset occurs or when a USB reset occurs and FRSTE is set to 1.

# 2.2 Device Operation

The operation of the TAS1020A is explained in the following sections. For additional information on USB, refer to the Universal Serial Bus Specification, Version 1.1.

# 2.2.1 Clock Generation

The TAS1020A requires an external 6-MHz crystal with load capacitors and PLL loop filter components to derive all the clocks needed for both USB and codec operation. Figure 4–1 shows the connection of these components to the TAS1020A. Figure 4–1 also shows a ground shield residing on the top layer of the PCB and underneath the crystal and its load capacitors and the PLL components. The PLL is an analog PLL, and noise pickup in these components can translate to phase jitter at the output of the PLL, which in turn can translate to distortion at the codec. A ground shield is recommended to attenuate the digital noise components on the board as seen at the PLL.

The AV<sub>SS</sub> and AV<sub>DD</sub> pins on the TAS1020A are used exclusively to power the analog PLL. To maintain isolation from the digital noise residing on a board, AV<sub>SS</sub> should be a separate ground plane that connects to the primary ground plane (DGND) at a single point via a ferrite bead. The ferrite bead should exhibit around 9  $\Omega$  of impedance at 100 MHz. AV<sub>DD</sub> should also be distinct from DV<sub>DD</sub>. A recommended architecture is to generate DV<sub>DD</sub> and AV<sub>DD</sub> from the same regulator line, with each derived from a RC filter in series with the regulator output. It is finally recommended that the ground shield for the crystal and its load capacitors and the PLL loop filter components be connected to AV<sub>SS</sub> at a single point via a ferrite bead of the same type as above.

Using the low frequency 6-MHz crystal and generating the required higher frequency clocks internally in the TAS1020A is a major advantage with regard to EMI.

## 2.2.2 Boot Process

The TAS1020A can boot from EEPROM or execute a host boot. Host boot will be used in the following circumstances:

- No EEPROM is present.

- An EEPROM is present, but does not contain a valid header.

- An EEPROM is present, but is a device EEPROM (contains header information only).

#### 2.2.2.1 EEPROM Boot Process

If the target device has an application EEPROM (an EEPROM that contains both header and application data), and if the header portion of the EEPROM content is valid, the EEPROM application code is downloaded to on-chip RAM. During the download process, the RAM is mapped to data space, and the boot code that orchestrates the download is part of the on-chip firmware housed in on-chip ROM. Also, while the application code is being downloaded, the TAS1020A remains disconnected from the USB bus.

When the download is complete, the firmware sets the ROM disable bit SDW. The setting of this bit maps the RAM from data space to program space, starting address 0x0000. Having set bit SDW, the firmware then branches to address 0x0000, which is the reset entry point for the application code. The application code is now running.

The application code then switches on the PUR output. The PUR output pin is connected, through a resistor, to the positive (DP) line of the differential USB bus. Switching PUR on informs the host that a full speed (12 Mb/s) device is present on the bus. In the enumeration procedure that follows, the application code reports its run-time device descriptor set. Following enumeration, the device is actively running its application.

#### 2.2.2.2 Host Boot Process

The DFU code in the TAS1020A fully adheres to the USB Device Class Specification for DFU 1.0. In addition, the TAS1020A utilizes the communication protocols from the DFU specification to implement a *host boot* capability for those applications that do not have an EEPROM resource. In such cases, the TAS1020A, at power-up, reports its DFU mode descriptor set rather than its run-time descriptor set and directly enters what the DFU specification terms the DFU Program Mode. The host processor must be cognizant of the fact that the device under enumeration does not have an EEPROM resource with valid code, and is already in the DFU mode awaiting a download per the DFU protocol. All of this capability is provided by the ROM-based code (firmware) that resides on the TAS1020A.

Specifically, the host boot process addresses three cases—an EPROM is not present, an EEPROM is present but the data in the EEPROM is invalid, or an EEPROM is present but the EEPROM is a device EEPROM (contains only

header data). In all three of these cases, the TAS1020A firmware comes up in the DFU Program Mode. A host boot ensues, but the final destination of the download depends on the status of the onboard EEPROM.

- If the firmware determines that no EEPROM is present (by noting, when addressing the EEPROM, the

absence of an acknowledge from the EEPROM), a Vendor ID of 0xFFFF and a Product ID of 0xFFFE is

reported during enumeration. The download that follows enumeration is written to the on-chip RAM. The

download from the host must include a header (see Section 2.2.2.3.1), and the *header overwrite* bit in the

header downloaded must be set to 0. (The *header overwrite* bit is used to instruct the TAS1020A firmware

as to whether or not the header portion of the download is to be written into the EEPROM. Since, in this case,

no EEPROM is present, this *header overwrite* bit must be set to 0). It is noted that the host must have prior

knowledge that the target will initialize in the DFU program mode and will require a download of application

code (and header) to RAM.

- If the firmware determines that an EEPROM is present (acknowledges are received from the EEPROM), but that the header data in the EEPROM is invalid, a Vendor ID of 0xFFFF and a Product ID of 0xFFFE is reported during enumeration. The download that follows enumeration is written to EEPROM. Since the EEPROM data was invalid, the host has to set the *header overwrite* bit in the header portion of the download to a 1 to ensure that the header is written to the EEPROM. It is noted that the host must have prior knowledge that the target does have an EEPROM, but that the data in the EEPROM is invalid. This could be a situation such as the initial download of the application on a production line.

- If the firmware determines that an EEPROM is present, that the header data in the EEPROM is valid, but that the header data in the EEPROM indicates that the EEPROM is a *device* EEPROM, the Vendor ID and Product ID settings in the EEPROM-resident header is reported during enumeration. In addition, the strings in the header, if applicable, are reported. The EEPROM download that follows enumeration will be written to the on-chip RAM facility. In addition to download image to the EEPROM. If the host does not wish to overwrite the valid header data in the EEPROM, it must set the *header overwrite* bit in its download header to a 0. It is noted that the host must have knowledge that the target contains an EEPROM, and that the EEPROM.

#### 2.2.2.3 EEPROM Data Organization

Two types of data can be stored in the EEPROM—header data, which contains USB device information, and application code. The presence of header data in the EEPROM is mandatory, but the presence of application code is optional.

# 2.2.2.3.1 EEPROM Header

Table 2–1 shows the format and information contained it the header data. As seen from Table 2–1, the header data begins at address 0x0000 in the EEPROM and precedes the application code.

| OFFSET | TYPE               | SIZE | VALUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|--------|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0      | headerChksum       | 1    | Header check sum—derived by adding the header data, excluding the header checksum, in bytes, and retaining the lower byte of the sum as the checksum.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 1      | HeaderSize         | 1    | Size, in units of bytes, of the header including strings if applied                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 2      | Signature          | 2    | Signature: 0x1234                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 4      | VendorID           | 2    | JSB Vendor ID<br>JSB Product ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 6      | ProductID          | 2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 8      | ProductVersion     | 1    | oduct version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 9      | FirmwareVersion    | 1    | Firmware version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 10     | UsbAttributes      | 1    | <ul> <li>USB attributes:</li> <li>Bit 0: If set to 1, the header includes all three strings: language, manufacture, and product strings, if set to 0, the header does not include any string. The strings, if present, must conform to the USB string format per USB spec 1.0 or later.</li> <li>Bit 1 : Not used.</li> <li>Bit 2: If set to 1, the device can be self powered, if set to 0, cannot be self powered.</li> <li>Bit 3: If set to 1, the device can be bus powered, if set to 0, cannot be bus powered.</li> <li>Bit 4 7: Reserved</li> </ul>                         |  |  |  |

| 11     | MaxPower           | 1    | Maximum power the device needs in units of 2 mA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 12     | Attributes         | 1    | <ul> <li>Device attributes:</li> <li>Bit 0: If set to 1, the CPU clock is 24 MHz, if set to 0, the CPU clock is 12 MHz.</li> <li>Bit 1: If set to 1, the download version of the header will be written into the EEPROM (download target has to be EEPROM). If the header is not to be overwritten, or if the target is RAM, this bit must be cleared to 0.</li> <li>Bit 2: Not used.</li> <li>Bit 3: If set to 1, the EEPROM can support a 400 kHz I<sup>2</sup>C bus, if set to 0, the EEPROM cannot support a 400 MHz I<sup>2</sup>C bus.</li> <li>Bit 4 7: Reserved</li> </ul> |  |  |  |

| 13     | WPageSize          | 1    | Maximum I <sup>2</sup> C write page size, in units of bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 14     | DataType           | 1    | This value defines if the device is an application EEPROM or a device EEPROM.<br>0x01: Application EEPROM—contains header and application code.<br>0x02: Device EEPROM—contains only header.<br>All other values are invalid.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 15     | RpageSize          | 1    | Maximum I <sup>2</sup> C read page size, in units of bytes. If the value is zero, the whole payLoadSize is read in one I <sup>2</sup> C read setup.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 16     | payLoadSize        | 2    | Size, in units of bytes, of the application, if using EEPROM as an application EEPROM, otherwise the value is 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| XXXX   | Language string    | 4    | Language string in standard USB string format if applied. If this attribute is applied, the two attributes that follow must also be applied. If this attribute is not applied, the following two attributes cannot be applied.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| XXXX   | Manufacture string |      | Manufacture string in standard USB string format if applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

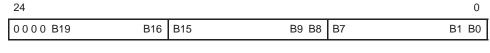

| XXXX   | Product string     |      | Product string in standard USB string format if applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |