# THCV213 and 214

LVDS SerDes transmitter and receiver

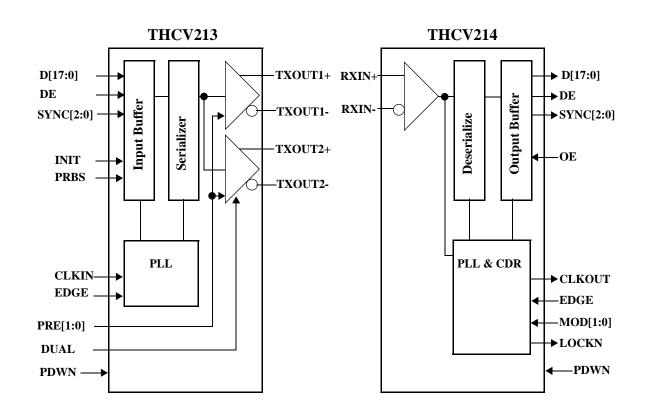

## General Description

THCV213 and 214 are designed to support pixel data transmission between the Host and Display. The chipset can transmit 18bit data and 4bit control data through only a single differential cable at a pixel clock frequency from 5MHz to 40MHz.

By V-by-One® technologies, unique encoding scheme and proprietary CDR technique, a link synchronization is achieved without any external frequency reference such as a crystal oscillator. It drastically improves the cost and space of PCBs of a display system.

THCV213 transmitter converts input data into a single LVDS serial data stream with the embedded clock. It supports pre-emphasis for a long cable transmission. 214 receiver extracts the clock from the embedded clock and transforms the serial data stream back into the parallel data.

To confirm the reliability of the link, several functions are supported. THCV213 can transmit the SYNC pat-

tern which expedites the link establishment. 214 has an indicator of its PLL status.

#### Features

- Transmit 18bit data and 4bit control data via a single differential cable

- Wide frequency range: 5MHz to 40MHz

- Support SYNC pattern and LOCK indicator

- Pre Emphasis mode

- Clock edge selectable

- Dual Display mode

- Power Down mode

- Low power single 3.3V CMOS design

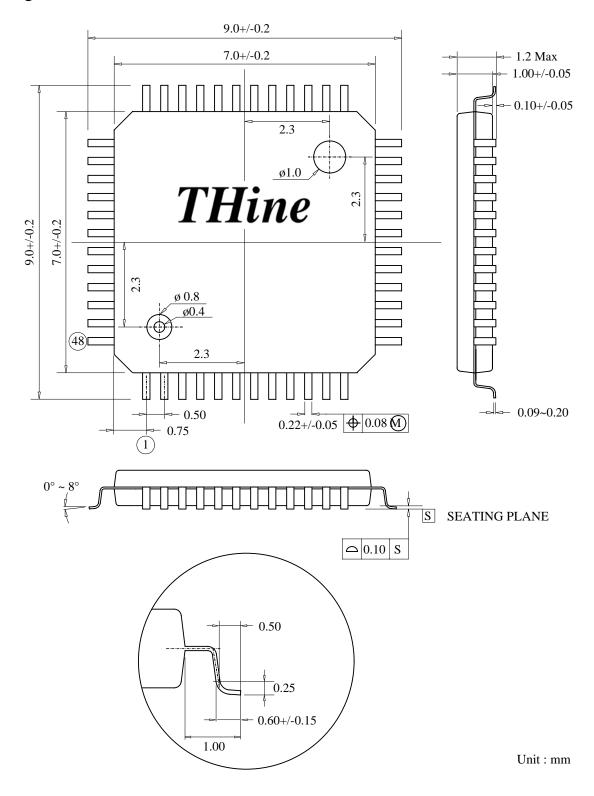

- 48pin TQFP

#### Block Diagram

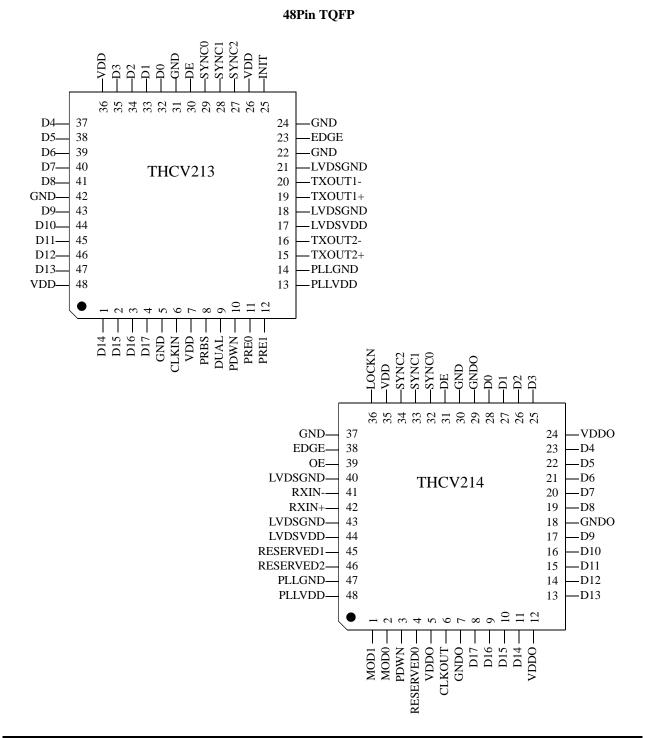

#### Package Information

| PART         | TEMP. RANGE   | PACKAGE    |

|--------------|---------------|------------|

| THCV213-1TTN | 0°C to 70°C   | 48pin TQFP |

| THCV214-1TTN | 0°C to 70°C   | 48pin TQFP |

| THCV213-5TTN | -40°C to 85°C | 48pin TQFP |

| THCV214-5TTN | -40°C to 85°C | 48pin TQFP |

#### Pin Out

Copyright©2010 THine Electronics, Inc.

# Pin Description

# THCV213 Pin Description

| Pin Name            | Pin #                             | type    | Description                                                                                                                                            |  |  |  |

|---------------------|-----------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TXOUT1-,<br>TXOUT1+ | 20, 19                            | LVDSOUT | LVDS output.                                                                                                                                           |  |  |  |

| TXOUT2-,<br>TXOUT2+ | 16, 15                            | LVDSOUT | LVDS output for Dual Display mode.<br>Identical to TXOUT1+/<br>Hi-Z when Normal operation.                                                             |  |  |  |

| D0~D17              | 32~35,<br>37~41,<br>43~47,<br>1~4 | IN      | Data input.<br>Active if input DE=High                                                                                                                 |  |  |  |

| SYNC2~SYNC0         | 27~29                             | IN      | Sync input.<br>Active if input DE =Low.<br>Input sync data pulse must be wider than or equal to<br>two input clock periods.                            |  |  |  |

| DE                  | 30                                | IN      | Data Enable (DE) input.<br>Refer to Tabe2 for requirements.                                                                                            |  |  |  |

| CLKIN               | 6                                 | IN      | Clock input.<br>5 MHz to 40MHz.                                                                                                                        |  |  |  |

| PDWN                | 10                                | IN      | H: Normal operation.<br>L: Power Down, TXOUT1+/-, (TXOUT2+/-) are Hi-Z.                                                                                |  |  |  |

| EDGE                | 23                                | IN      | Input clock triggering edge select.<br>H: Rise edge, L: Fall edge.                                                                                     |  |  |  |

| PRE0,PRE1           | 11, 12                            | IN      | Select the level of pre-emphasis.PRE1PRE0DescriptionLLw/o Pre-EmphasisLHw/ 25% Pre EmphasisHLw/ 50% Pre EmphasisHHw/ 100% Pre Emphasis                 |  |  |  |

| INIT                | 25                                | IN      | <ul> <li>H: Triggers SYNC pattern output fromTXOUT1+/- and<br/>(TXOUT2+/-), normally used in Shake Hand mode.</li> <li>L: Normal operation.</li> </ul> |  |  |  |

| DUAL                | 9                                 | IN      | <ul> <li>H: Dual Display mode</li> <li>Both TXOUT1-/+ and TXOUT2-/+ enabled.</li> <li>L: Normal operation</li> <li>Only TXOUT1-/+ enabled.</li> </ul>  |  |  |  |

| Pin Name | Pin #      | type  | Description                                    |

|----------|------------|-------|------------------------------------------------|

|          |            |       | H: Internal test pattern generator is enabled. |

|          |            |       | Pseud-Random Bit Sequence (PRBS) is generated  |

| PRBS     | 8          | IN    | and is fed into input data latches.            |

|          |            |       | Normally used for debug.                       |

|          |            |       | L: Normal operation.                           |

| VDD      | 7,26,36,48 | Power | Power supply pins for digital circuitry.       |

| GND      | 5,22,24,   | Power | Crownd mine for divited singuitary             |

| GND      | 31,42,     | Power | Ground pins for digital circuitry.             |

| LVDSVDD  | 17         | Power | Power supply pin for LVDS input.               |

| LVDSGND  | 18, 21     | Power | Ground pins for LVDS input.                    |

| PLLVDD   | 13         | Power | Power supply pin for PLL circuitry.            |

| PLLGND   | 14         | Power | Ground pin for PLL circuitry.                  |

# 214 Pin Description

| Pin Name     | Pin #                              | type   | Description                                                                                                                                                            |

|--------------|------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXIN-, RXIN+ | 41, 42                             | LVDSIN | LVDS input.                                                                                                                                                            |

| D17~D0       | 8~11,<br>13~17,<br>19~23,<br>25~28 | OUT    | Data outputs.                                                                                                                                                          |

| SYNC0~SYNC2  | 32~34                              | OUT    | Sync output.                                                                                                                                                           |

| DE           | 31                                 | OUT    | Data Enable (DE) output.                                                                                                                                               |

| CLKOUT       | 6                                  | OUT    | Clock output.                                                                                                                                                          |

| LOCKN        | 36                                 | OUT    | Lock detect output.<br>H: Unlock, L: Lock.<br>Can be used as an input signal detector, too.                                                                            |

| PDWN         | 3                                  | IN     | <ul><li>H: Normal operation.</li><li>L: Power Down, all outputs except LOCKN and CLK-<br/>OUT are held low. Refer to Fig9 for details(Note1.)</li></ul>                |

| EDGE         | 38                                 | IN     | Output clock triggering edge select.<br>H: Rise edge, L: Fall edge.                                                                                                    |

| OE           | 39                                 | IN     | Output Enable.<br>(DE, SYNC0~SYNC2, D0~D17,CLKOUT)<br>H: Output disabled, all outputs are Hi-Z.<br>L: Output enabled. (Note1)                                          |

| MOD1, MOD0   | 1, 2                               | IN     | Select operation mode<br>Both must be tied to GND.<br>MOD0       MOD1         L       L         Normal Mode         Shake Hand Mode         Others       Not Available |

| RESERVED0    | 4                                  | IN     | Must be tied to GND.                                                                                                                                                   |

| RESERVED1    | 45                                 | IN     | Must be tied to LVDSGND.                                                                                                                                               |

| RESERVED2    | 46                                 | IN     | Must be tied to LVDSGND.                                                                                                                                               |

| VDD          | 35                                 | Power  | Power supply pin for digital circuitry.                                                                                                                                |

| GND          | 30,37                              | Power  | Ground pins for digital circuitry.                                                                                                                                     |

| LVDSVDD      | 44                                 | Power  | Power supply pin for LVDS input.                                                                                                                                       |

| LVDSGND      | 40,43                              | Power  | Ground pins for LVDS input.                                                                                                                                            |

| PLLVDD       | 48                                 | Power  | Power supply pin for PLL circuitry.                                                                                                                                    |

| PLLGND       | 47                                 | Power  | Ground pin for PLL circuitry.                                                                                                                                          |

| VDDO         | 5,12,24                            | Power  | Power supply pins for TTL output.                                                                                                                                      |

| GNDO         | 7,18,29                            | Power  | Ground pins for TTL output.                                                                                                                                            |

Note1: The state of outputs determined by the combination of OE and PDWN is as follow

| OE | PDWN | Output State                                                                                                                                                             |

|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L  | Н    | Normal Operation.                                                                                                                                                        |

| L  | L    | All outputs except LOCKN and CLKOUT are held low.<br>LOCKN is held high while CLKOUT is driven high when EDGE input is<br>high and is driven low when EDGE input is low. |

| Н  | Н    | All outputs are Hi-Z.                                                                                                                                                    |

| Н  | L    | All outputs are Hi-Z.                                                                                                                                                    |

## Table 1 Output State determined by OE and PDWN

## Table 2Requirements for DE input

| Operation<br>Mode | DE = High                                                                 | DE = Low                                                    |

|-------------------|---------------------------------------------------------------------------|-------------------------------------------------------------|

| Normal            | Min. 2t <sub>TCIP</sub> (See Fig5 for t <sub>TCIP</sub> )<br>Max. 80 µsec | Min. 50 t <sub>TCIP</sub> (See Fig5 for t <sub>TCIP</sub> ) |

| ShakeHand         | Min. $2t_{TCIP}$ (See Fig5 for $t_{TCIP}$ )                               | Min. 2t <sub>TCIP</sub> (See Fig5 for t <sub>TCIP</sub> )   |

## Absolute Maximum Ratings

| Supply Voltage (V <sub>DD</sub> ) | -0.3V ~ +4.0V                |

|-----------------------------------|------------------------------|

| CMOS/TTL Input Voltage            | $-0.3V \sim (V_{DD} + 0.3V)$ |

| CMOS/TTL Output Voltage           | $-0.3V \sim (V_{DD} + 0.3V)$ |

| LVDS Receiver Input Voltage       | $-0.3V \sim (V_{DD} + 0.3V)$ |

| Output Current                    | -30mA ~ 30mA                 |

| Junction Temperature              | +125°C                       |

| Storage Temperature Range         | -55°C ~+125°C                |

| Reflow Peak Temperature / Time    | +260°C / 10sec.              |

| Maximum Power Dissipation @+25°C  | 1.9W                         |

## Operation Condition

| Parameter                     | Consumer |      |      |      |      |      |       |

|-------------------------------|----------|------|------|------|------|------|-------|

|                               | Min.     | Тур. | Max. | Min. | Тур. | Max. | Units |

| All Supply Voltage            | 3.0      | 3.3  | 3.6  | 3.0  | 3.3  | 3.6  | V     |

| Operating Ambient Temperature | 0        |      | 70   | -40  |      | 85   | °C    |

#### **Electrical Characteristics**

#### CMOS/TTL DC Specifications

## Transmitter: V<sub>DD</sub>=VDD=LVDSVDD=PLLVDD, Receiver: V<sub>DD</sub>=VDD=VDDO=LVDSVDD=PLLVDD

| Symbol           | Parameter                    | Conditions                 | Min. | Тур. | Max.            | Units |

|------------------|------------------------------|----------------------------|------|------|-----------------|-------|

| V <sub>IH</sub>  | High Level Input Voltage     |                            | 2.0  |      | V <sub>DD</sub> | V     |

| V <sub>IL</sub>  | Low Level Input Voltage      |                            | GND  |      | 0.8             | V     |

| V <sub>OH</sub>  | DH High Level Output Voltage | $V_{DD} = 3.0V \sim 3.6V$  | 2.4  |      |                 | V     |

| * OH             |                              | $I_{OH} = -4mA$            |      |      |                 | v     |

| V <sub>OL</sub>  | Low Level Output Voltage     | $V_{DD} = 3.0V \sim 3.6V$  |      |      | 0.4             | v     |

| * OL             | Low Level Output voltage     | $I_{OL} = 4mA$             |      |      | 0.4             | v     |

| I <sub>IIL</sub> | Input Leak Current           | $0V \le V_{IN} \le V_{CC}$ |      |      | ±10             | μΑ    |

## THCV213 DC Specifications

#### V<sub>DD</sub>=VDD=LVDSVDD=PLLVDD

| Symbol          | Parameter                                         | Conditions                                         | Min.  | Тур. | Max.  | Units |

|-----------------|---------------------------------------------------|----------------------------------------------------|-------|------|-------|-------|

| VOD             | Differential Output Voltage                       | RL=100Ω, PRE<1:0>=L,L                              | 250   | 350  | 450   | mV    |

| ΔVOD            | Change in VOD between complementary output states | RL=100Ω, PRE<1:0>=L,L                              |       |      | 35    | mV    |

| VOC             | Common Mode Voltage                               | RL=100Ω, PRE<1:0>=L,L                              | 1.125 | 1.25 | 1.375 | V     |

| ΔVOC            | Change in VOC between complementary output states | RL=100Ω, PRE<1:0>=L,L                              |       |      | 35    | mV    |

| I <sub>OS</sub> | Output Short Circuit Current                      | V <sub>OUT</sub> =0V,RL=100Ω                       |       |      | 24    | mA    |

| I <sub>OZ</sub> | Output TRI-STATE Current                          | PDWN=L,<br>V <sub>OUT</sub> =0V to V <sub>DD</sub> |       |      | ±10   | μΑ    |

# 214 DC Specifications

#### V<sub>DD</sub>=VDD=VDDO=LVDSVDD=PLLVDD

| Symbol           | Parameter                          | Conditions            | Min. | Тур. | Max. | Units |

|------------------|------------------------------------|-----------------------|------|------|------|-------|

| V <sub>TH</sub>  | Differential Input High Threshold  | VIC = +1.2V           |      |      | 100  | mV    |

| V <sub>TL</sub>  | Differential Input Low Threshold   | VIC – +1.2 V          | -100 |      |      | mV    |

| I                | Differential Input Leakage Cument  | $V_{IN} = +2.4 V/0 V$ |      |      | 10   | A     |

| I <sub>ILD</sub> | Differential Input Leakage Current | $V_{DD} = 3.6V$       |      |      | ±10  | μA    |

# THCV213 Supply Current

V<sub>DD</sub>=VDD=LVDSVDD=PLLVDD

| Symbol             | Parameter                                | Condition                 | Тур. | Max. | Units |

|--------------------|------------------------------------------|---------------------------|------|------|-------|

|                    | Transmitter Supply Current               | Normal Operation          |      |      |       |

| I <sub>TCCW1</sub> | (Worst Case Pattern)                     | f <sub>CLKIN</sub> =40MHz |      | 60   | mA    |

|                    | (Fig. 1)                                 | V <sub>DD</sub> =3.3V     |      |      |       |

|                    | Transmitter Supply Current               | Dual Display Mode         |      |      |       |

| I <sub>TCCW2</sub> | (Worst Case Pattern)                     | f <sub>CLKIN</sub> =40MHz |      | 90   | mA    |

|                    | (Fig. 1)                                 | V <sub>DD</sub> =3.3V     |      |      |       |

| I <sub>TCCS</sub>  | Transmitter Power Down<br>Supply Current | PDWN = L                  |      | 10   | μΑ    |

#### 214 Supply Current

#### V<sub>DD</sub>=VDD=VDDO=LVDSVDD=PLLVDD

| Symbol            | Parameter                                  | Condition                   | Тур. | Max. | Units |

|-------------------|--------------------------------------------|-----------------------------|------|------|-------|

|                   | Receiver Supply Current                    | f <sub>CLKOUT</sub> = 40MHz |      |      |       |

| I <sub>RCCW</sub> | (Worst Case Pattern) V <sub>DD</sub> =3.3V |                             |      | 70   | mA    |

|                   | (Fig. 1)                                   | CL=8pF (Fig. 4)             |      |      |       |

| I <sub>RCCS</sub> | Receiver Power Down                        | PDWN = L                    |      | 10   | μΑ    |

|                   | Supply Current                             | PDWIN = L                   |      |      |       |

#### Worst Case Pattern

Fig. 1 Test Pattern

# Switching Characteristics

# THCV213 Switching Characteristics

|                     | -                                                    |                        | V <sub>DD</sub> =VD                | D=LVDSVDD=I                         | PLLVDD |

|---------------------|------------------------------------------------------|------------------------|------------------------------------|-------------------------------------|--------|

| Symbol              | Parameter                                            | Min.                   | Тур.                               | Max.                                | Units  |

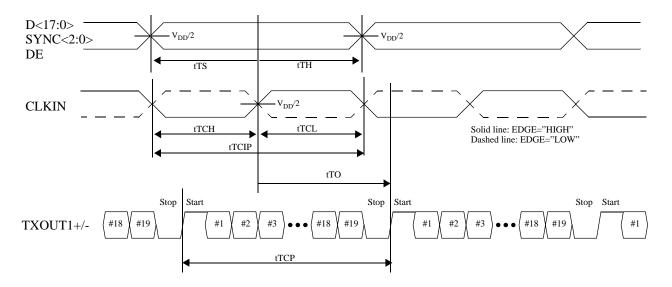

| t <sub>TCIP</sub>   | CLKIN Period (Fig. 5)                                | 25                     |                                    | 200                                 | ns     |

| t <sub>TCP</sub>    | TXOUT Period (Fig. 5)                                |                        | t <sub>TCIP</sub>                  |                                     | ns     |

| t <sub>TCH</sub>    | CLKIN High Time (Fig. 5)                             | 0.35t <sub>TCIP</sub>  | 0.5t <sub>TCIP</sub>               | 0.65t <sub>TCIP</sub>               | ns     |

| t <sub>TCL</sub>    | CLKIN Low Time (Fig. 5)                              | 0.35t <sub>TCIP</sub>  | 0.5t <sub>TCIP</sub>               | 0.65t <sub>TCIP</sub>               | ns     |

| t <sub>TS</sub>     | TTL Data Setup to CLKIN (Fig. 5)                     | 5                      |                                    |                                     | ns     |

| t <sub>TH</sub>     | TTL Data Hold from CKLIN (Fig. 5)                    | 0                      |                                    |                                     | ns     |

| t <sub>TO</sub>     | CLK IN to TXOUT+/- Delay (Fig. 5)                    | $3\frac{17}{21}$ tTCIP |                                    | $3\frac{17}{21}t_{\text{TCIP}} + 7$ | ns     |

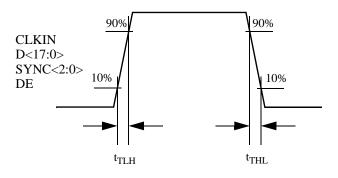

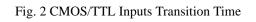

| t <sub>TLH</sub>    | TTL Input Low to High Transition Time<br>(Fig. 2)    |                        | 3.0                                | 5.0                                 | ns     |

| t <sub>THL</sub>    | TTL Input High to Low Transition Time (Fig. 2)       |                        | 3.0                                | 5.0                                 | ns     |

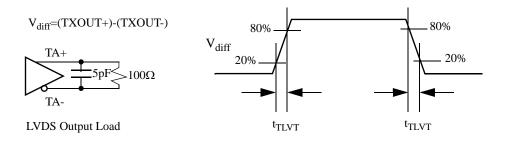

| t <sub>TLVT</sub>   | LVDS Differential Output Transition<br>Time (Fig. 3) |                        | 0.6                                | 1.5                                 | ns     |

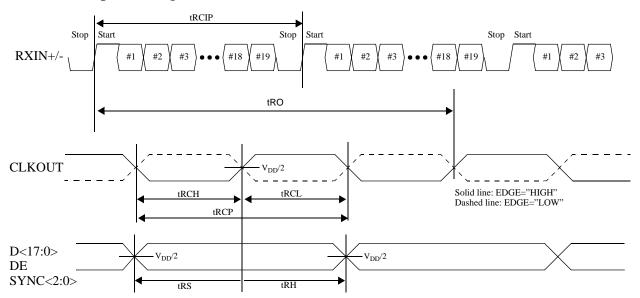

| t <sub>TPLL</sub>   | Phase Lock Loop Set Time (Fig. 7)                    |                        |                                    | 10.0                                | ms     |

| t <sub>THZ</sub>    | PDWN Low to Output Hi-Z Set Delay<br>(Fig. 7)        |                        | 3.6                                |                                     | ns     |

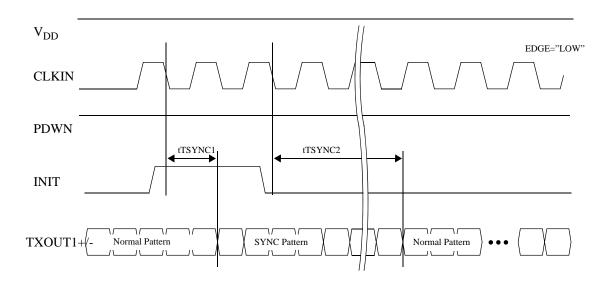

| t <sub>TSYNC1</sub> | INIT High to Sync Pattern Output Delay<br>(Fig. 8)   |                        | $\frac{17}{21}t_{\text{TCIP}} + 3$ |                                     | ns     |

| t <sub>TSYNC2</sub> | INIT Low to Normal Pattern Output<br>Delay (Fig. 8)  |                        | $1026\frac{17}{21}t_{TCIP} + 3$    |                                     | ns     |

# 214 Switching Characteristics

#### V<sub>DD</sub>=VDD=VDDO=LVDSVDD=PLLVDD

| Symbol             | Parameter                                                     | Min.                          | Тур.                | Max.                          | Units           |

|--------------------|---------------------------------------------------------------|-------------------------------|---------------------|-------------------------------|-----------------|

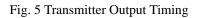

| t <sub>RCIP</sub>  | RXIN Period (Fig. 6)                                          | 25                            |                     | 200                           | ns              |

| t <sub>RCP</sub>   | CLKOUT Period (Fig. 6)                                        |                               | t <sub>RCIP</sub>   |                               | ns              |

| t <sub>RCH</sub>   | CLKOUT High Time (Fig. 6)                                     |                               | $\frac{t_{RCP}}{2}$ |                               | ns              |

| t <sub>RCL</sub>   | CKLOUT Low Time (Fig. 6)                                      |                               | $\frac{t_{RCP}}{2}$ |                               | ns              |

| t <sub>RS</sub>    | TTL Data Setup to CLKOUT (Fig. 6)                             | 0.3t <sub>RCP</sub>           |                     |                               | ns              |

| t <sub>RH</sub>    | TTL Data Hold from CKLOUT (Fig. 6)                            | 0.3t <sub>RCP</sub>           |                     |                               | ns              |

| t <sub>RO</sub>    | RXIN+/- to CLKOUT Delay (Fig. 6)                              | $4\frac{13.5}{21}t_{\rm RCP}$ |                     | $4\frac{13.5}{21}t_{RCP} + 7$ | ns              |

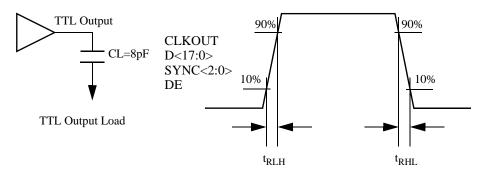

| t <sub>RLH</sub>   | TTL Output Low to High Transition Time (Fig. 4)               |                               | 3.0                 | 5.0                           | ns              |

| t <sub>RHL</sub>   | TTL Output High to Low Transition Time (Fig. 4)               |                               | 3.0                 | 5.0                           | ns              |

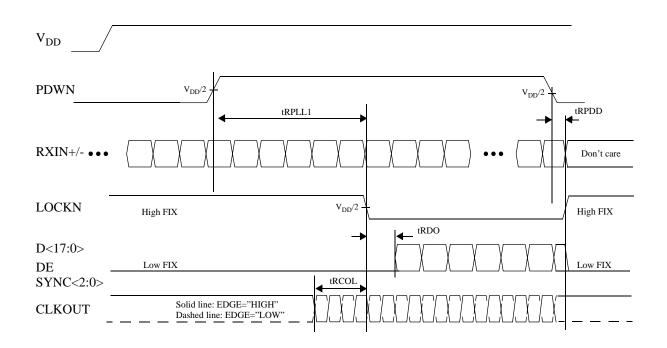

| t <sub>RPLL1</sub> | Phase Lock Loop Set (Fig. 9)                                  |                               |                     | 10.0                          | ms              |

| t <sub>RPDD</sub>  | Power-Down Delay (Fig. 9)                                     |                               | 9                   |                               | ns              |

| t <sub>RDO</sub>   | LOCKN transition to TTL Data Output<br>Delay (Fig. 9)         |                               | 2                   |                               | clock<br>cycles |

| t <sub>RCOL</sub>  | Beginning of Clock Output to LOCKN<br>transition Time(Fig. 9) | 10                            |                     |                               | clock<br>cycles |

| t <sub>RLCS</sub>  | LOCKN transition to Stop of Clock Out-<br>put Time(Fig. 9)    | 3                             |                     |                               | clock<br>cycles |

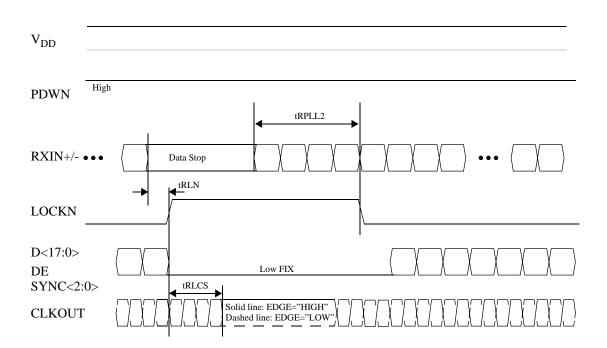

| t <sub>RPLL2</sub> | Phase Lock Loop Set (Fig. 10)                                 |                               |                     | 10.0                          | ms              |

| t <sub>RLN</sub>   | Data Stop to LOCKN Transition Delay<br>(Fig. 10)              |                               | 7                   |                               | ns              |

Fig. 3 LVDS Outputs Transition Time

**Receiver Output Switching Characteristics**

## AC Timing Diagram and Test Circuits (Continued)

### Transmitter Output timing

## Receiver Output timing

Fig. 6 Receiver Output Timing

#### AC Timing Diagram and Test Circuits (Continued)

#### Transmitter Start-up and Power-down Sequence

#### Fig. 7 Transmitter Start-up and Power-down Sequence

## Transmitter Lock Recovery Sequence

Fig. 8 Transmitter Lock Recovery Sequence

#### AC Timing Diagram and Test Circuits (Continued)

Receiver Start-up and Power-down Sequence

#### Fig. 9 Receiver Start-up and Power-down Sequence

#### **Receiver Lock Recovery Sequence**

Fig. 10 Receiver Lock Recovery Sequence

#### **Detailed Description**

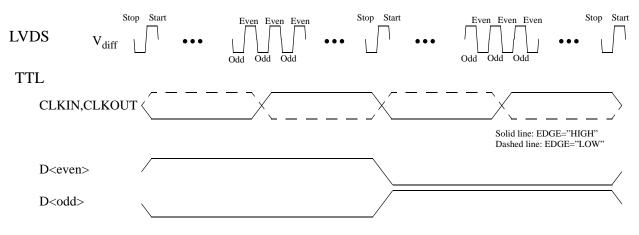

With V-by-One®'s proprietary encoding scheme and CDR (Clock and Data Recovery) architecture, THCV213 and THCV214 enable transmission of 18bit video signals (D17 to D0) and 4 bit control signals (SYNC2 to SYNC0, and DE) by a single differential pair cable with minimal external components. THCV214, the receiver, can seamlessly operate for a wide range of a parallel clock frequency of 5MHz to 40MHz, detecting the frequency of an incoming data stream, and recovering both the clock and data by itself. It does not need any external frequency reference, such as a crystal oscillator.

THCV213 serializes video signals and control signals separately, depending on the polarity of Data Enable (DE) input. DE is a signal which indicates whether video or control signals are active. When DE input is high, it serializes D17 to D0 inputs into a single differential data stream. And it transmits serialized control signals (SYNC2 to SYNC0) when DE input is low.

THCV214 automatically extracts the clock from the incoming data stream and converts the serial data into 18 bit parallel data with DE being high or three control signals with DE being low, recognizing which type of serial data is being sent by the transmitter.

#### **Operation Mode**

In order to accommodate various types of data format or to expedite the link establishment between the transmitter and receiver, THCV214 has two modes of operation, namely Normal mode and Shake Hand mode.

#### Normal Mode

The Normal mode operation is the one described above in "Detailed Description." This mode fully utilizes the chipset's capability, enabling the transmission of 18 video and 4bit control signals. It is required to have DE signal which indicates whether video or control signals are active.

#### Shake Hand Mode

This mode requires an extra wire connecting THCV214's LOCKN and THCV213's INIT pin. This wire does not need to be impedance controlled one. While the link is not being established between the transmitter and receiver, the receiver's LOCKN is driven low, telling the transmitter to send a special set of data pattern which eases connection between the two. The chipset automatically enters the Shake Hand mode, once THCV214's LOCKN pin and THCV213's INIT pin are connected together.

If there is no DE signal, THCV213/214 can still work in the Shake Hand mode with the transmitter's DE input tied high. In this case, the amount of data transmission reduces to 18 bit digital signals (D17 to D0.)

#### **DE** Requirement

There are some requirements for DE signal if the chipset is to be used in the Normal mode as described in Table 2.

#### DE Requirements for Normal Mode

The length of DE being low is at least 50 clock cycle long. The maximum time of DE being high is 80us, the minimum of DE=L is 2 clock cycles.

#### THCV213 Power Down (PDWN)

Setting the PDWN pin low results in THCV213 in the Power Down mode. All the internal circuitry turns off and the TXOUT+/- outputs turn to Hi-Z. Refer to Fig. 7

#### THCV213 EDGE

The polarity of the EDGE pin selects which edge (rising or falling) of the input clock by which the input data are latched in. When EDGE is set high, the transmitter uses the rising edge of the input clock to take in the input data. When EDGE is low, it takes in the data at the falling edge of the clock. Select its polarity so that the transmitter latches in the data with better setup/hold time margin.

### THCV213 Pre-Emphasis (PRE1,0)

Pre-emphasis can equalize severe signal degradation caused by long distance or high-speed transmission. Two pins, PRE1 and PRE0, select the strength of preemphasis.

| PRE1 | PRE0 | Description          |

|------|------|----------------------|

| L    | L    | w/o Pre-Emphasis     |

| L    | Н    | w/ 25% Pre Emphasis  |

| Н    | L    | w/ 50% Pre Emphasis  |

| Н    | Н    | w/ 100% Pre Emphasis |

#### THCV213 INIT

Driving the INIT pin high forces the transmitter to send a special set of pattern called SYNC pattern, which makes it easier for the receiver to recover the clock and data. This function is normally used in the Shake Hand mode with a wire connecting the transmitter INIT pin and the receiver LOCKN pin.

It can also be used to expedite the link establishment in the Normal mode by driving the INIT pin high at power up, forcing the transmitter to output the SYNC pattern for a certain amount of time in order to train the receiver.

# THCV213 Dual Display Mode (DUAL)

THCV213 has two high speed output buffers so that it can be used in an application where a video source wants to send the same data to two displays. The DUAL pin activates the Dual Display mode.

#### THCV213 PRBS

Setting the PRBS pin high enables the internal test pattern generator. It generates Pseudo-Random Bit Sequence of  $2^{23}$ -1.

The generated PRBS is fed into input data latches, formatted as VGA video like data, encoded and serialized into TXOUT output.

This function is normally to be used for analyzing the signal integrity of the transmission channel including PCB traces, connectors, and cables.

# THCV214 Lock/Input Detect (LOCKN)

When the PLL of THCV214 has locked to the incoming data stream, it drives LOCKN low. And then TTL/ CMOS outputs become valid. This LOCKN signal can also be used as an indicator of whether the incoming data is valid or not.

This pin is to be connected to the transmitter INIT pin with a cable in the Shake Hand mode.

#### THCV214 Power Down (PDWN)

Setting the PDWN pin low results in THCV214 in the Power Down mode. All the internal circuitry and input buffers turn off, and all outputs except LOCKN and CLKOUT are held low. The LOCKN pin is driven high when in the Power Down mode. The CLKOUT is fixed one way or the other depending on the EDGE input. Refer to Fig. 9.

#### THCV214 EDGE

The polarity of the EDGE pin selects which edge (rising or falling) of the output clock by which the output data are latched out. When EDGE is set high, the receiver uses the falling edge of the output clock to put out the data so that the next-stage chip can use the rising edge of the clock to latch in the data with the maximum setup/hold time margin, and vice versa. Select its polarity according to the next-stage chip input characteristics.

#### THCV214 Output Enable (OE)

The OE pin can disable TTL/CMOS outputs and place them in Hi-Z. Thus THCV214's TTL/CMOS outputs can be bused so that the receiver can be used in an application where there are multiple video sources and one display.

#### THCV214 MOD1,0

Both MOD1 and MOD0 must be tied to GND. The receiver enters into an appropriate operation mode by itself.

#### Cables and Connectors

In a system with high speed digital signals, a special care must be taken to avoid loss and degradation of the signals due to limited bandwidth and impedance mismatch along the transmission line. Characteristic impedance of PCB traces, cables, and connectors must be tightly controlled.

Use cables that have a differential characteristic impedance of  $100\Omega$ . Shielded twisted pair cables are recommended for increasing noise immunity and lowering EMI.

Connectors are recommended that cause minimum discontinuities in terms of characteristic impedance and geometry of the transmission path.

#### PCB Layout Considerations

Use a four-layer PCB with signal, ground, power, and signal assigned for each layer. PCB traces for high-speed signals (TXOUT, RXIN) must be microstrip lines with a differential impedance of  $100\Omega$ . Route differential signal traces symmetrically. Avoid right angle turns of the high speed traces because they usually cause impedance discontinuity.

Place a 100  $\Omega$  termination resistor between RXIN+ and RXIN- as close to the receiver as possible to reduce reflection.

Separate all the power domains in order to avoid unwanted noise coupling between noisy digital and sensitive analog domains. Use high frequency ceramic capacitors of 10nF or  $0.1\mu$ F as bypass capacitors between power and ground pins. Place them as close to each power pin as possible. A  $4.7\mu$ F capacitor in parallel with the smaller capacitor to PLLVDD is recommended for the receiver.

# Package

#### Notices and Requests

- 1. The product specifications described in this material are subject to change without prior notice.

- 2. The circuit diagrams described in this material are examples of the application which may not always apply to the customer's design. We are not responsible for possible errors and omissions in this material. Please note if errors or omissions should be found in this material, we may not be able to correct them immediately.

- 3. This material contains our copy right, know-how or other proprietary. Copying or disclosing to third parties the contents of this material without our prior permission is prohibited.

- 4. Note that if infringement of any third party's industrial ownership should occur by using this product, we will be exempted from the responsibility unless it directly relates to the production process or functions of the product.

- 5. This product is presumed to be used for general electric equipment, not for the applications which require very high reliability (including medical equipment directly concerning people's life, aerospace equipment, or nuclear control equipment). Also, when using this product for the equipment concerned with the control and safety of the transportation means, the traffic signal equipment, or various Types of safety equipment, please do it after applying appropriate measures to the product.

- 6. Despite our utmost efforts to improve the quality and reliability of the product, faults will occur with a certain small probability, which is inevitable to a semi-conductor product. Therefore, you are encouraged to have sufficiently redundant or error preventive design applied to the use of the product so as not to have our product cause any social or public damage.

- 7. Please note that this product is not designed to be radiation-proof.

- 8. Customers are asked, if required, to judge by themselves if this product falls under the category of strategic goods under the Foreign Exchange and Foreign Trade Control Law.