Mobilygen Corporation 2900 Lakeside Drive #100 Santa Clara, CA 95054 Tel: (408) 869-4000 Fax: (408) 980-8044 email: info@mobilygen.com

# MG1264 User Manual

Low Power H.264 and AAC codec

#### Copyright © 2004, 2005 Mobilygen Corporation

Mobilygen and the Mobilygen logo are registered trademarks of Mobilygen Corporation, Inc. All rights reserved.

All other products and services mentioned in this publication are the trademarks, service marks, registered trademarks, or registered servicemarks of their respective owners.

Document Version: 0.8

Mobilygen Corporation 2900 Lakeside Drive #100 Santa Clara, CA 95054

Telephone1 (408) 869-4000FAX1 (408) 980 8044

www.mobilygen.com

#### **About This Document**

This manual provides a complete reference for the MG1264 Low Power H.264 and AAC Codec for Mobile Devices User Manual.

#### Audience

This document assumes that the reader has knowledge of:

- Mobile Video product architectures

- Video Standards

#### Conventions

The following conventions were used in this manual:

| Courier typface          | .ini file             | Code Listings, names of files, symbols, and directo-<br>ries, are shown in courier typeface.                              |

|--------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------|

| Bold Courier<br>typeface | install               | In a command line, keywords are shown in bold,<br>non-italic, Courier typeface. Enter them exactly as<br>shown.           |

| Italics                  | Note:                 | Notes about the subject are shown with a header in italics.                                                               |

| Bold Italics             | Important:            | Important information about the subject is shown with the header in bold Italics. This information should not be ignored. |

| Square Brackets          | [version]             | You may, but need not, select one item enclosed within brackets. Do not enter the brackets                                |

| Angle Brackets           | <username></username> | You must provide the information enclosed within brackets. Do not enter the brackets                                      |

| Bar                      | les   les.out         | You may select one (but not more than one) item from a list separated by bars. Do not enter the bars.                     |

When computer output listings are shown, an effort has been made not to break up the lines when at all possible. This is to improve the clarity of the printout; for this reason, some listings will be indented, and others will start at the left edge of the column.

#### Terms

#### H.264

This manual makes reference to the term H.264 and MPEG4 Part 10 Advanced Video Coding (AVC). The full name for the standard is ITU-T Rec. H.264 / ISO/IEC 11496-10, "Advanced Video Coding", and information can be found on the standard at:

• <u>http://www.iec.ch/</u>

The H.264 standard was jointly developed by the Video Coding Experts Group (VCEG) of the International Telecommunications Union (ITU) and the MPEG committee of ISO/IEC. The two identical standards are ISO MPEG4 Part 10 of MPEG4, and ITU-T H.264, but it is commonly referred to as "Advanced Video Coding" or AVC.

#### AAC

AAC is the MPEG-4 Advanced Audio Coding standard. Information on AAC can be found at:

• http://www.aac-audio.com/

### Table of Contents

| Chapter 1. Overview                                                | 13   |

|--------------------------------------------------------------------|------|

| 1.1: Architecture                                                  | . 14 |

| 1.2: MG1264 Codec Applications                                     | . 15 |

| 1.3: Features                                                      |      |

| 1.3.1: MG1264 Codec Specifications                                 | 17   |

| 1.3.2: H.264 Encoder Target Performance                            |      |

| 1.3.3: PAL Resolution H.264                                        |      |

| 1.3.4: SVGA 800x600 Video Resolution                               | 18   |

| 1.3.5: Video Input and Output Scaling                              | 18   |

| 1.3.6: User Control of H.264 Encoder Features (Tools)              |      |

| 1.3.7: The AAC Audio CODEC                                         |      |

| 1.3.8: I/O Control                                                 |      |

| Chapter 2. MG1264 Codec Host Interface                             | 21   |

| 2.1: MG1264 Codec Host Interface Physical Description              |      |

| 2.1.1: Connection Diagram                                          |      |

| 2.1.2: MG1264 Codec Host Interface Signals                         |      |

| 2.2: MG1264 Codec Host Interface Logical Description               |      |

| 2.2.1: System Control                                              |      |

| 2.2.2: Compressed Data I/O Through the MG1264 Codec Host Interface |      |

| 2.2.3: Interrupts                                                  |      |

| 2.2.4: DMA Channels                                                | 24   |

| 2.2.5: Latency Considerations                                      | 24   |

| 2.3: Read/Write Timing                                             | . 25 |

| 2.3.1: Read Timing Sequence in Read Enable Mode                    | 26   |

| 2.3.2: Write Data Timing in Write Enable Mode                      | 27   |

| 2.3.3: Read Timing Sequence in Read/Write and Enable Mode          | 28   |

| 2.3.4: Write Data Timing in Read/Write and Enable Mode             | 29   |

| 2.4: DMA Transfers                                                 | . 30 |

| 2.4.1: Pacing using the HDMAREQ Pin                                | 30   |

| 2.4.2: Pacing using the EMFifoRdReq/EMFifoWrReq Bits               | 30   |

| 2.4.3: Pacing using the HWAIT Pin                                  |      |

| 2.5: MG1264 Codec Register Indirect Access                         |      |

| 2.5.1: Reading a Register                                          |      |

| 2.5.2: Writing a Register                                          |      |

| 2.6: Programming the MG1264 Codec Host Interface                   |      |

| 2.6.1: Register Maps                                               |      |

| 2.7: Register Definitions                                          |      |

| 2.7.1: Configuration, Data, and Status Registers                   |      |

| 2.7.2: Peripheral Interrupt Registers                              |      |

| 2.7.3: Clock and Configuration Registers                           |      |

| 2.7.4: Accessing External Memory Port 1 and Port 2                 | 39   |

| 2.7.5: Reading the MG1264 Codec's External Memory                  | 39  |

|--------------------------------------------------------------------|-----|

| 2.7.6: Checking the FIFO Status                                    | 40  |

| 2.7.7: External Memory Access Registers                            | 41  |

| 2.7.8: Bitstream Write FIFO Access Registers                       | 47  |

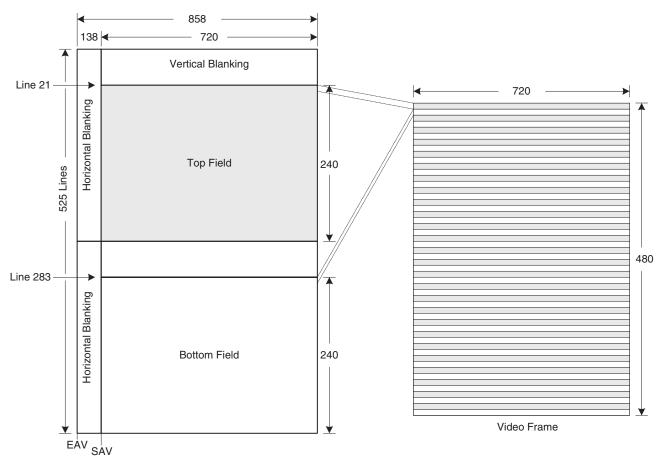

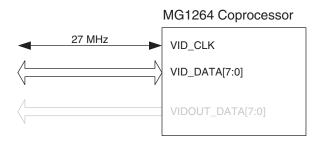

| Chapter 3. Video Interface                                         | 49  |

| 3.1: Video Interface Usage                                         | 50  |

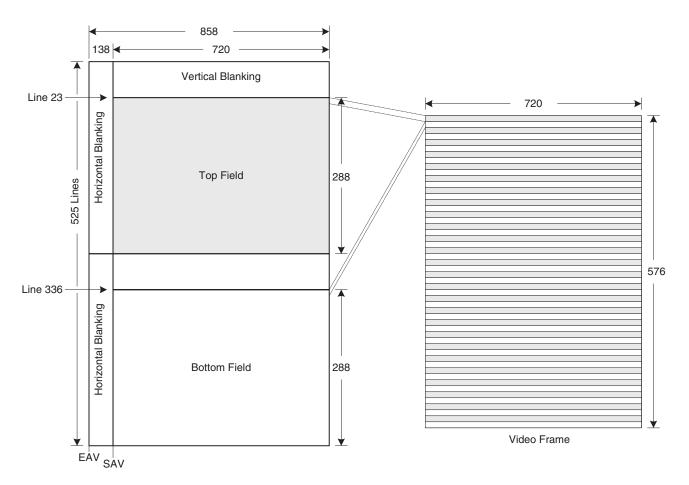

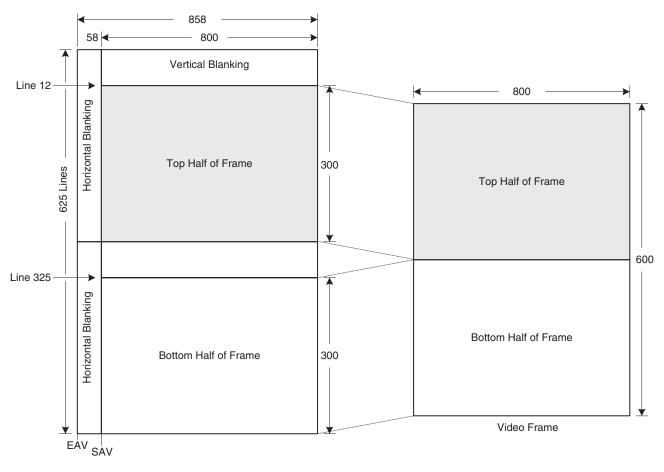

| 3.1.1: Interlaced ITU-RBT.656 Video Interfaces                     | 50  |

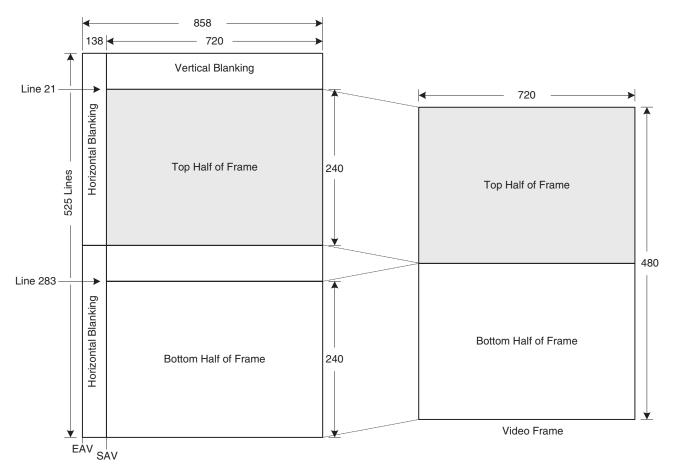

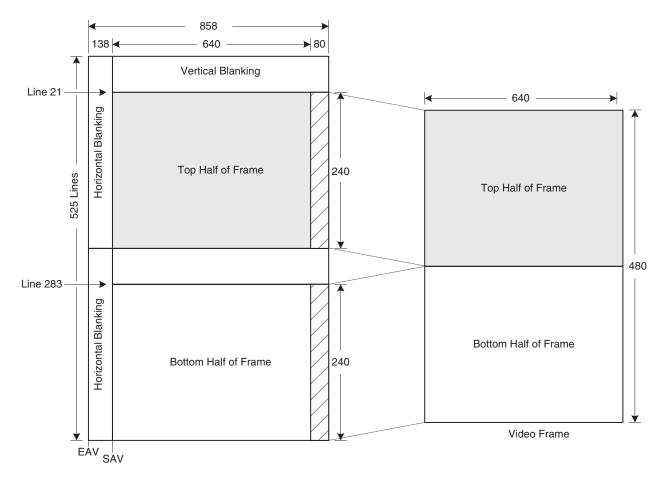

| 3.1.2: Progressive Video Interfaces for D1 Resolution and Below    | 52  |

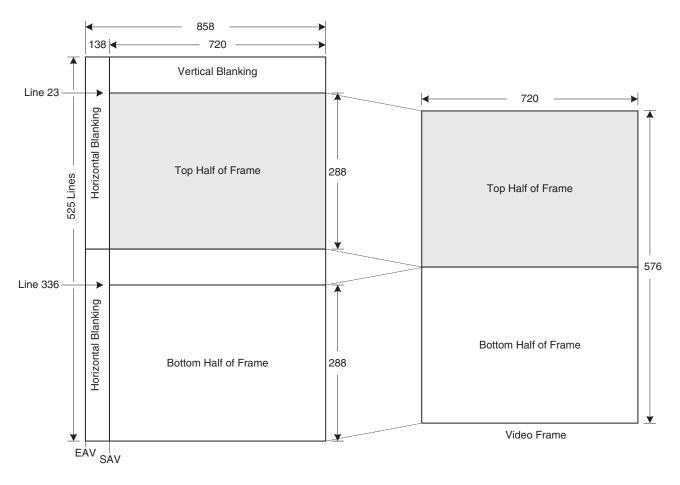

| 3.1.3: Progressive Video Interface for 800x600 (SVGA) and 768x576. | 55  |

| 3.2: Video Interface Signals                                       |     |

| 3.3: Video Interface Timing                                        | 56  |

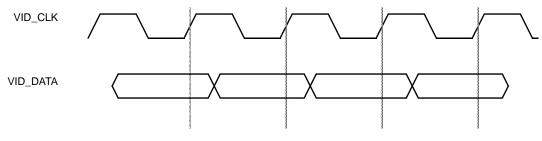

| Chapter 4. SDRAM Interface                                         | 57  |

| 4.1: The SDRAM Interface                                           | 57  |

| 4.2: Mobile SDRAM Features                                         | 59  |

| 4.2.1: Voltage Operation (3.3V, 2.5V, 1.8V)                        | 59  |

| 4.2.2: Temperature Compensated Self-Refresh                        | 59  |

| 4.2.3: Deep Power Down                                             | 59  |

| 4.2.4: Drive Strength Control                                      | 59  |

| Chapter 5. Audio Interface                                         | 61  |

| 5.1: Audio Interface Overview                                      | 61  |

| 5.2: Audio Interface Signals                                       | 62  |

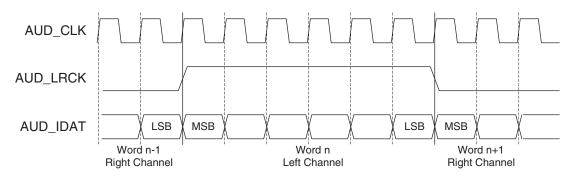

| 5.3: I2S Audio Waveforms                                           | 63  |

| 5.4: Left Justified Audio Waveform                                 | 64  |

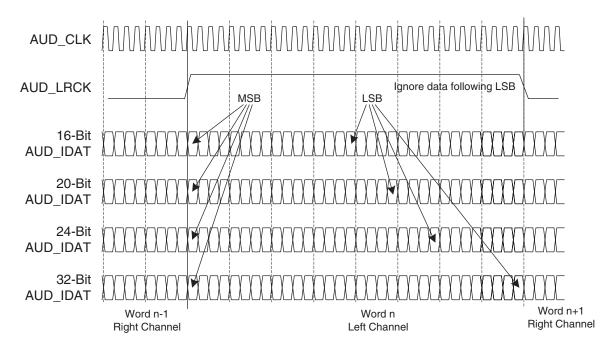

| 5.5: 16, 20, 24, 32-Bit Left Justified Audio Waveform              | 64  |

| Chapter 6. Miscellaneous Signals                                   | 65  |

| Chapter 7. Programming                                             | 67  |

| 7.1: Modes Of Operation                                            |     |

| 7.2: Power-Up and Initialization                                   |     |

| 7.3: Encode and Decode Mode                                        |     |

| Chapter 8. Bringing up the MG1264 Codec                            | 69  |

| 8.1: Decoder Bringup                                               |     |

| 8.1.1: Phase 1: Decoding a Small Elementary NAL Video Stream       |     |

| 8.1.2: Phase 2: Decoding a Large Elementary NAL Video Stream with  |     |

| ware Flow Control 73                                               |     |

| 8.1.3: Phase 3: Decoding A QBOX Stream                             | 76  |

| 8.2: Encoder Bringup                                               |     |

| 8.2.1: Phase 1: Recording a Small Elementary NAL Video Stream      |     |

| 8.2.2: Phase 2: Recording a Large Elementary NAL Video Stream with |     |

| ware Flow Control 80                                               | 0.1 |

| 8.2.3: Phase 3: Recording a QBOX Stream                            | 81  |

| Chapter 9. Firmware Loader                                   | 85   |

|--------------------------------------------------------------|------|

| 9.1: Firmware Image Format                                   | . 86 |

| 9.1.1: Header                                                |      |

| 9.1.2: Global Pointer Block                                  | 86   |

| 9.1.3: Pre-download CSR                                      | 86   |

| 9.1.4: Firmware                                              | . 87 |

| 9.1.5: Uninitialized Data                                    | 87   |

| 9.1.6: End                                                   | 88   |

| 9.2: Sample Code                                             |      |

| Chapter 10. Application Programming Interface                | 91   |

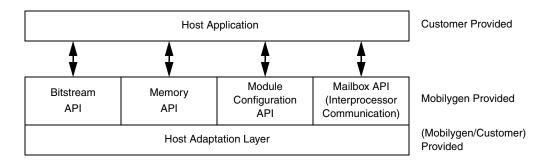

| 10.1: Host Interface and the Hardware Abstraction Layer      |      |

| 10.1.1: QHAL_EM                                              |      |

| 10.1.2: QHAL_MBOX                                            |      |

| 10.1.3: QHAL_BS                                              |      |

| 10.2: Media Processor Firmware Programming Model             |      |

| 10.2.1: Control Objects                                      |      |

| 10.2.2: Commands, Events, and Inter-Processor Communications |      |

| 10.2.3: Global Pointer Block                                 |      |

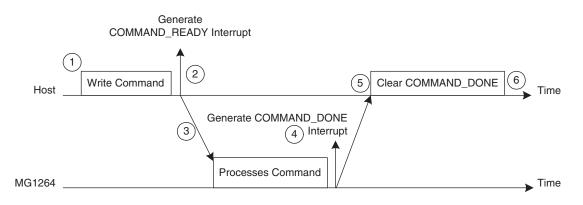

| 10.2.4: Sending a Command to the Firmware                    |      |

| 10.2.5: Reading Events from the Media Processor Firmware     |      |

| 10.2.6: Subscribing and Unsubscribing to Events              |      |

| 10.2.7: Configuration Parameters                             |      |

| 10.2.8: Status Block                                         |      |

| 10.3: Bitstream Formats                                      |      |

| 10.3.1: QBox Bitstream Format                                |      |

| 10.3.2: Elementary Video                                     |      |

| 10.4: System Control Interface Object                        |      |

| 10.4.1: Overview                                             |      |

| 10.4.2: Object ID                                            |      |

| 10.4.3: State Machine                                        |      |

| 10.4.4: Commands                                             |      |

| 10.4.5: Configuration Parameters                             |      |

| 10.4.6: Events                                               |      |

| 10.5: Status Block                                           |      |

| 10.5.1: heartbeat                                            |      |

| 10.5.2: droppedEvents                                        |      |

| 10.5.3: evReadWritePointers                                  |      |

| 10.5.4: pendingEvent                                         |      |

| 10.6: H.264/ACC Decoder Interface Object                     |      |

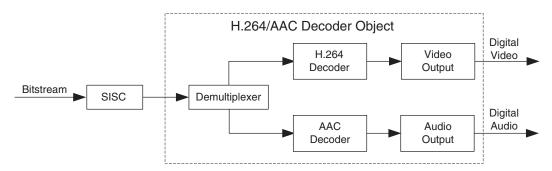

| 10.6.1: Overview                                             |      |

| 10.6.2: Logical View of the AV Decoder                       |      |

| 10.6.3: AV Decoder Features                                  |      |

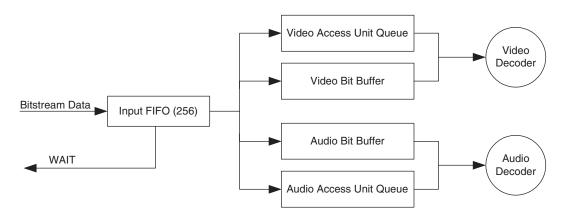

| 10.6.4: Sending Encoded Bitstreams to the Decoder            |      |

| 10.6.5: Object ID                                            |      |

| 10.6.6: State Machine                                        |      |

|                                                              | 110  |

| 10.6.7: Commands                                                                                                                   | 119                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 10.6.8: Configuration Parameters                                                                                                   | 126                                                                                      |

| 10.6.9: Events                                                                                                                     |                                                                                          |

| 10.6.10: Status Block                                                                                                              | 131                                                                                      |

| 10.6.11: Trick Play Techniques                                                                                                     | 132                                                                                      |

| 10.7: H.264/AAC Encoder Interface Object                                                                                           | 135                                                                                      |

| 10.7.1: Overview                                                                                                                   | 135                                                                                      |

| 10.7.2: Logical View of the AV Encoder                                                                                             | 135                                                                                      |

| 10.7.3: AV Encoder Features                                                                                                        |                                                                                          |

| 10.7.4: Receiving Encoded Bitstreams from the Encoder                                                                              | 136                                                                                      |

| 10.7.5: Controlling the Video Bitrate                                                                                              | 138                                                                                      |

| 10.7.6: Object ID                                                                                                                  | 139                                                                                      |

| 10.7.7: State Machine                                                                                                              |                                                                                          |

| 10.7.8: Commands                                                                                                                   | 140                                                                                      |

| 10.7.9: Configuration Parameters                                                                                                   | 144                                                                                      |

| 10.7.10: Events                                                                                                                    | 150                                                                                      |

|                                                                                                                                    |                                                                                          |

| 10.7.11: Status Block                                                                                                              | 151                                                                                      |

|                                                                                                                                    |                                                                                          |

| Chapter 11. Specifications                                                                                                         | 153                                                                                      |

| Chapter 11. Specifications                                                                                                         | <b> 153</b><br>154                                                                       |

| Chapter 11. Specifications<br>11.1: Electrical Characteristics<br>11.1.1: Absolute Maximum Ratings                                 | <b> 153</b><br>154<br>154                                                                |

| Chapter 11. Specifications<br>11.1: Electrical Characteristics<br>11.1.1: Absolute Maximum Ratings<br>11.1.2: Operating Conditions | <b> 153</b><br>154<br>154<br>154                                                         |

| Chapter 11. Specifications                                                                                                         | <b> 153</b><br>154<br>154<br>154<br>155                                                  |

| Chapter 11. Specifications                                                                                                         | <b> 153</b><br>154<br>154<br>154<br>155<br>155                                           |

| Chapter 11. Specifications                                                                                                         | <b></b> 153<br>154<br>154<br>154<br>155<br>155<br>155                                    |

| Chapter 11. Specifications                                                                                                         | <b></b> 153<br>154<br>154<br>154<br>155<br>155<br>155<br>156                             |

| Chapter 11. Specifications                                                                                                         | <b></b> 153<br>154<br>154<br>154<br>155<br>155<br>156<br>157                             |

| Chapter 11. Specifications                                                                                                         | <b></b> 153<br>154<br>154<br>155<br>155<br>155<br>156<br>157<br>160                      |

| Chapter 11. Specifications.<br>11.1: Electrical Characteristics                                                                    | <b></b> 153<br>154<br>154<br>155<br>155<br>155<br>156<br>157<br>160<br>161               |

| Chapter 11. Specifications                                                                                                         | <b></b> 153<br>154<br>154<br>155<br>155<br>155<br>156<br>157<br>160<br>161<br>163        |

| Chapter 11. Specifications.<br>11.1: Electrical Characteristics                                                                    | <b></b> 153<br>154<br>154<br>155<br>155<br>155<br>156<br>157<br>160<br>161<br>163<br>164 |

### List of Figures

| MG1264 Codec Block Diagram                                                                                          | 14                |

|---------------------------------------------------------------------------------------------------------------------|-------------------|

| H.264/AVC Tools/Profiles                                                                                            | 15                |

| Camera System-Level Block Diagram                                                                                   | 16                |

| MG1264 Codec Host Interface Connection Diagrams                                                                     |                   |

| Register Logical View                                                                                               | 23                |

| Read Access Timing in Read Enable Mode                                                                              | 26                |

| Write Access Timing in Write Enable Mode                                                                            |                   |

| Read Access Timing in Read/Write and Enable Mode                                                                    | 28                |

| Write Access Timing in Read/Write and Enable Mode                                                                   |                   |

| ITU-R BT.656 NTSC Interlaced Video Standard                                                                         | 50                |

| ITU-R BT.656 PAL Interlaced Video Standard                                                                          | 51                |

| NTSC Progressive Video                                                                                              | 52                |

| PAL Progressive Video                                                                                               | 53                |

| 640 x 480 Progressive Video                                                                                         |                   |

| 800 x 600 (SVGA) Progressive Video                                                                                  | 55                |

| Video Interface Connections                                                                                         | 56                |

| Video Interface Timing                                                                                              | 56                |

| MG1264 Codec SDRAM Interface                                                                                        | 58                |

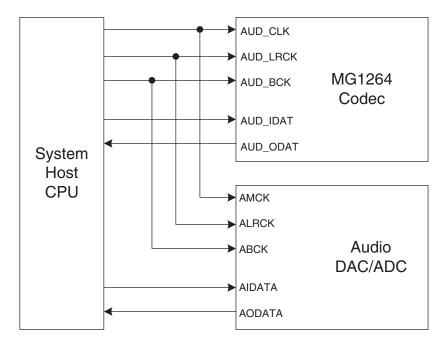

| Audio Interface Connections with the System Host CPU as the Audio Clock M                                           | laster            |

| 62                                                                                                                  |                   |

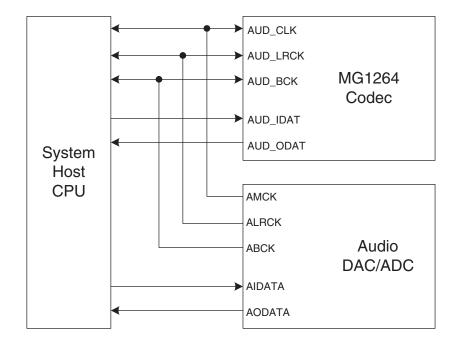

| Audio Interface Connections with the DAC/ADC as the Audio Clock Master $% \mathcal{A}$ .                            | 63                |

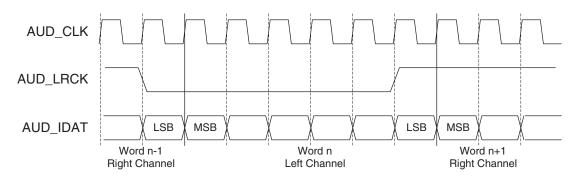

| I2S Left-justified Audio Waveform                                                                                   | 63                |

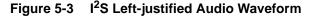

| Left-justified Audio Waveform                                                                                       |                   |

| 16, 20, 24, and 32-Bit Left Justified Audio Waveform                                                                |                   |

| QHAL Structure                                                                                                      |                   |

| Command Transfer Timing                                                                                             | 98                |

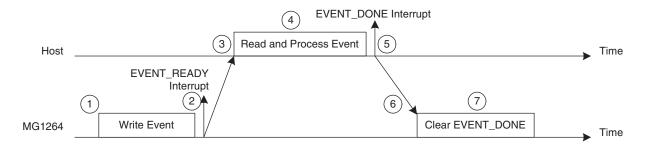

| Event Transfer Timing                                                                                               |                   |

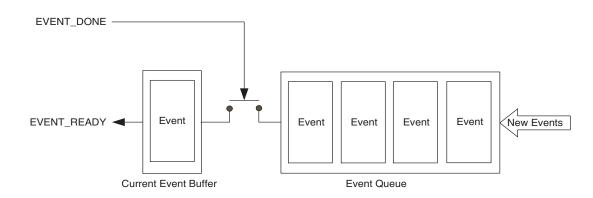

| Event Queuing                                                                                                       |                   |

| Idealized Decoder Datapath                                                                                          |                   |

| Decoder Buffer Structure                                                                                            |                   |

| Idealized Encoder Datapath                                                                                          |                   |

| Circular Buffer Management of Bitstream Blocks                                                                      |                   |

| MG1264 Codec Host Interface AC Timing Waveform                                                                      |                   |

| MG1264 Codec HDMAREQ Timing                                                                                         |                   |

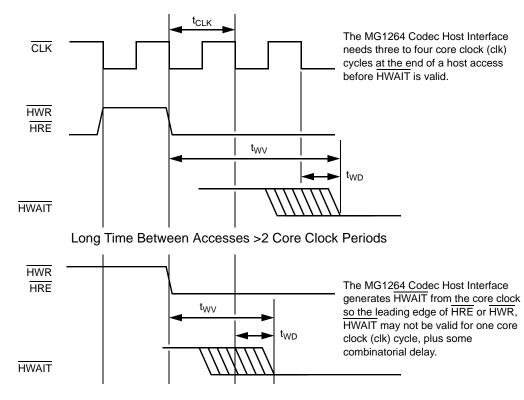

| HWAIT Timing                                                                                                        |                   |

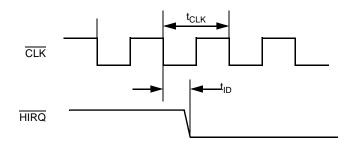

| HIRQ Timing                                                                                                         |                   |

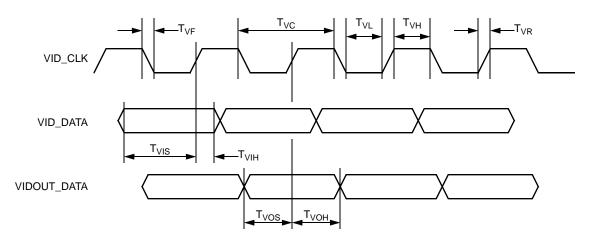

| Video Interface Timing Diagram                                                                                      |                   |

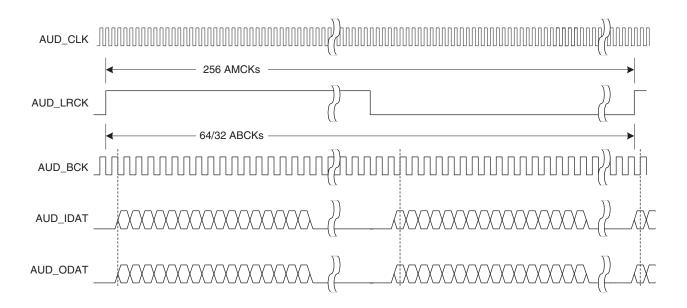

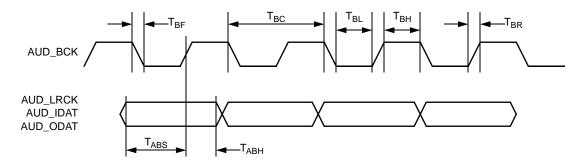

| Audio Timing Diagram                                                                                                | 161               |

| And's Interfere Time in Discourse                                                                                   |                   |

| Audio Interface Timing Diagram                                                                                      | 161               |

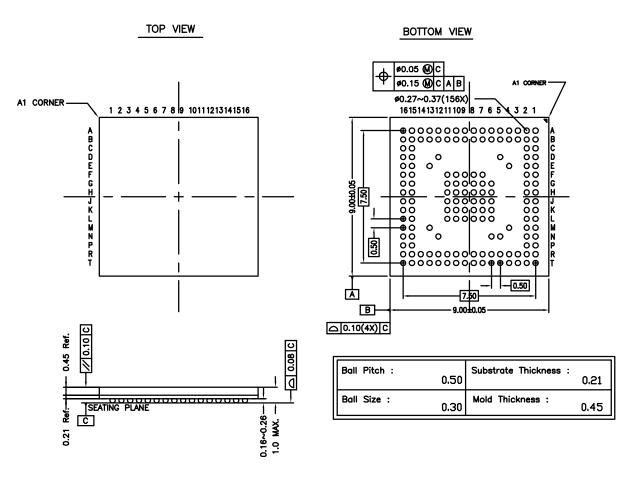

| MG1264 Codec Pinout Diagram                                                                                         | 161<br>164        |

| MG1264 Codec Pinout Diagram<br>MG1264 Codec Pinout Diagram (Continued)<br>156-pin BGA Package Mechanical Dimensions | 161<br>164<br>165 |

### List of Tables

| H.264 Video Bitrates and Resolutions for NTSC                 | 17  |

|---------------------------------------------------------------|-----|

| H.264 Video Bitrates and Resolutions for PAL                  |     |

| AAC Encoder Features                                          |     |

| MG1264 Codec Host Interface Pin Descriptions                  |     |

| MG1264 Codec Register and External Memory Device Register Map |     |

| Input Video Resolutions                                       |     |

| Video Interface Signals                                       |     |

| DRAM Interface Signal List                                    | 57  |

| AAC Encoder Features                                          | 61  |

| Audio Interface Signal List                                   |     |

| Miscellaneous Signals                                         | 65  |

| Forward State                                                 | 118 |

| Backward State                                                | 118 |

| Absolute Maximum Ratings                                      | 154 |

| Operating Conditions                                          | 154 |

| DC Characteristics                                            | 155 |

| Host Interface Timing                                         | 159 |

| Video Interface AC Timing Values                              |     |

| Audio Interface AC Timing Values                              | 162 |

| MG1264 Codec Pin List Sorted Alphabetically                   | 166 |

| MG1264 Codec Pin List by Side                                 | 168 |

|                                                               |     |

## Chapter 1. Overview

The MG1264 is a single-chip H.264 VGA codec IC that enables mobile products to capture, play and share video with three times the processing power of competing devices, while using substantially less power. The MG1264 is a complete A/V codec solution including both a H.264 VGA 30 frames-per-second video codec, and a high fidelity two-channel AAC audio codec. Power consumption while encoding is 185mW for the complete device including VGA 30fps video, 2-channel AAC audio, and all chip I/O functions.

Mobilygen has developed a unique chip architecture dedicated to low power video processing. The patented EVE (Enabling Video Everywhere) architecture was used to implement the MG1264 and includes the following key technologies:

- Dedicated hardware media processing engines that are active only when data is being processed

- A highly-optimized hardware multi-threaded embedded microcontroller with single cycle context switching that controls all media processing operations and allows for easy integration of customer differentiating features

- An advanced video pre-processor that greatly improves H.264 encoder efficiency and overall video quality

- An ultra-efficient video processing oriented memory controller with forward seeking transaction reordering capabilities that doubles memory efficiency allowing all functions to operate with a single 16-bit SDRAM

- Patented low-power H.264 video coding algorithms developed specifically to maximize video quality

- Easy to control through standard firmware APIs; no customer programming is required

The MG1264 is designed for use in still cameras, video cameras, cell phones with integral cameras, personal media players, peripheral products, and any other applications that require H-264 encoding and/or decoding capabilities with very low power consumption.

#### 1.1 Architecture

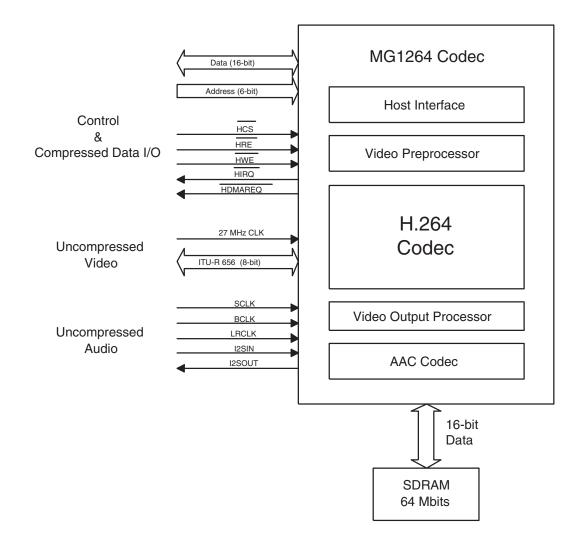

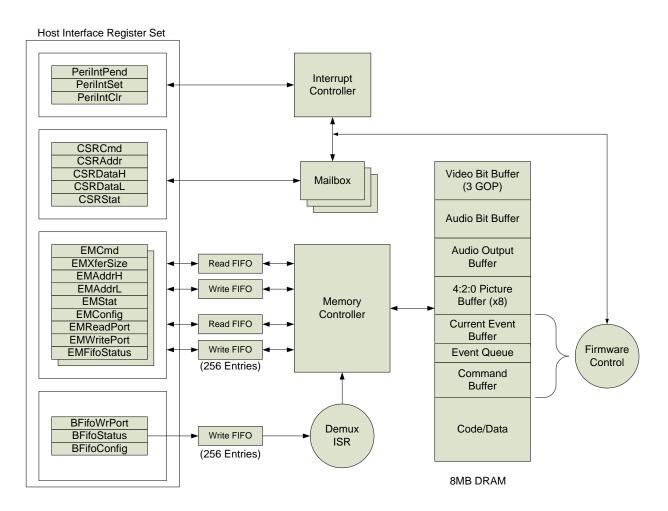

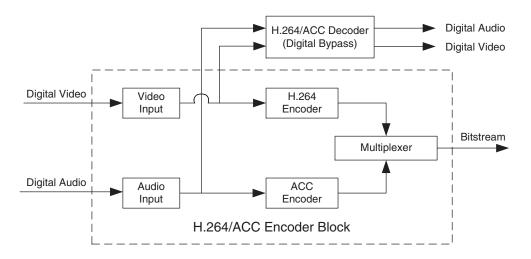

The MG1264 Low Power H.264 and AAC Codec for Mobile Devices is built of the following blocks as shown in Figure 1-1:

- MG1264 Codec Host Interface

- Video Input and Preprocessor (VPP)

- H.264 Video Codec

- Video Output Processor (VPU)

- AAC Audio CODEC

Figure 1-1 MG1264 Codec Block Diagram

#### 1.2 MG1264 Codec Applications

The MG1264 Low Power H.264 and AAC Codec for Mobile Devices is a VGA 30 fps H.264 and two-channel AAC Audio CODEC that enables Audio and Video (A/V) capture and playback functionality in mobile video products.

These include:

- Digital Still Cameras

- Solid-State Camcorders

- Portable Media Players

- Camera-enabled Cellular Phones

The MG1264 Codec produces syntactically correct A/V bitstreams that can be decoded by any standard-compliant decoder that incorporates support for H.264 and AAC playback such as software decoders on a PC.

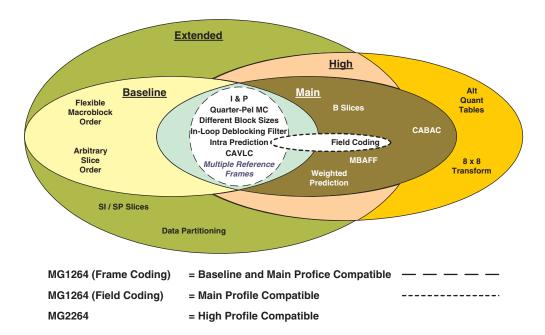

The MG1264 Codec is designed for low power operation. Mobile video products based on the MG1264 Codec can play back any A/V content that it captures, just like a traditional tape based camcorder. It can also play back any H.264 encoded stream using the tools we support. Figure 1-2 shows the MG1264 Codec's capabilities.

Figure 1-2 H.264/AVC Tools/Profiles

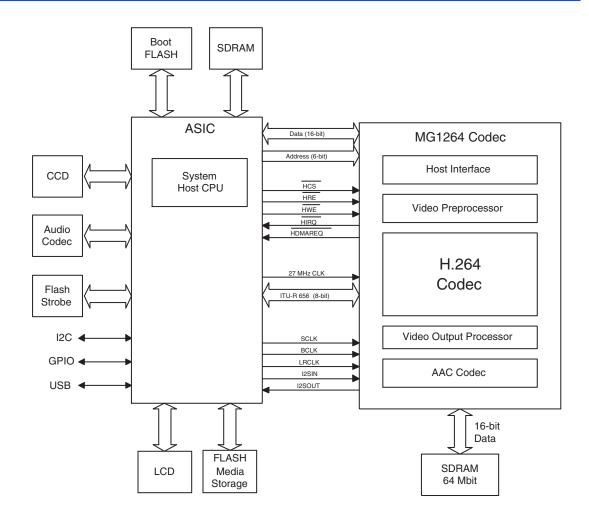

The MG1264 Codec is designed to be a coprocessor to a main System Host Processor and ASIC. Figure 1-3 is a camera system block diagram that shows how MG1264 Codec is integrated into a system. The main camera ASIC performs the traditional camera functions such as interface to the CCD, color processing, zoom lens control, LCD display, storage, etc.

Figure 1-3 Camera System-Level Block Diagram

#### 1.3 Features

The MG1264 Low Power H.264 and AAC Codec for Mobile Devices has these features:

#### 1.3.1 MG1264 Codec Specifications

The MG1264 Codec implements a subset of H.264 tools that achieves superior video quality with a low power budget. The MG1264 Codec does not implement the following H.264 tools: B-frames, CABAC, MAFF, ASO, and FMO.

The MG1264 Codec can be best classified in the following way: If Frame mode coding is used, then the MG1264 Codec produces Baseline and Main Profile compatible streams (see Figure 1-2 on page 15). Baseline is the primary encoding mode for the MG1264 Codec because today all DSC sensors use progressive scan CCDs, however the MG1264 Codec also supports Field mode coding. Streams coded as Field mode fall within the Main Profile.

The decoder in the MG1264 Codec decodes only streams created with the same subset of tools as listed above. For Baseline Profile, ASO and FMO are not widely used, so the primary limitation is in picture resolution (maximum 800x600x25 fps) and bitrate (10 Mbps).

#### 1.3.2 H.264 Encoder Target Performance

The MG1264 Codec is capable of standard definition full resolution (720x480 or 640x480) video encoding. While resolution down sampling can provide excellent visual results for video encoding at lower bitrates, the product emphasis is on full resolution.

Table 1-1 lists target bitrates and corresponding resolutions for NTSC.

| Video Bitrate<br>(kbps) | Horizontal<br>Resolution<br>(Pixels) | Vertical<br>Resolution<br>(Pixels) | fps <sup>a</sup> | Notes Regarding The Source Video                   |

|-------------------------|--------------------------------------|------------------------------------|------------------|----------------------------------------------------|

| 300                     | 320                                  | 240                                | 30               | QVGA, progressive, square pixel sensor             |

| 500                     | 640                                  | 240                                | 30               | Half-vertical, progressive, square pixel sensor    |

| 1000                    | 640                                  | 480                                | 30               | VGA, progressive, square pixel sensor              |

| 1500                    | 640                                  | 480                                | 30               | VGA, progressive, square pixel sensor              |

| 2000                    | 640                                  | 480                                | 30               | VGA, progressive, square pixel sensor              |

| 3000                    | 640                                  | 480                                | 30               | VGA, progressive, square pixel sensor              |

| 3000                    | 640                                  | 720                                | 30               | HD-M                                               |

| 3000                    | 800                                  | 600                                | 25               | SVGA, progressive, square pixel sensor             |

| 300                     | 352                                  | 240                                | 30               | SIF, progressive, rectangular pixel sensor         |

| 500                     | 720                                  | 240                                | 30               | Half-vertical, interlace, rectangular pixel sensor |

| 1000                    | 720                                  | 480                                | 30               | D1, interlace, rectangular pixel sensor            |

| 1500                    | 720                                  | 480                                | 30               | D1, interlace, rectangular pixel sensor            |

| 2000                    | 720                                  | 480                                | 30               | D1, interlace, rectangular pixel sensor            |

| 3000                    | 720                                  | 480                                | 30               | D1, interlace, rectangular pixel sensor            |

#### Table 1-1 H.264 Video Bitrates and Resolutions for NTSC

a. 30 fps is a shorthand representation for the traditional 29.976 NTSC frame rate. In applications where display on a traditional TV is required, the frame rate should be set accordingly.

#### 1.3.3 PAL Resolution H.264

The MG1264 Codec is also capable of PAL encoding, as shown in Table 1-2.

|  | Video<br>Bitrate<br>(kbps) | Horizontal<br>Resolution<br>(pixels) | Vertical<br>Resolution<br>(Pixels) | fps | Notes Regarding The Source Video                     |

|--|----------------------------|--------------------------------------|------------------------------------|-----|------------------------------------------------------|

|  | 300                        | 352                                  | 288                                | 25  | QSIF, progressive, rectangular pixel sensor          |

|  | 500                        | 720                                  | 288                                | 25  | Half-vertical, progressive, rectangular pixel sensor |

|  | 1000                       | 720                                  | 576                                | 25  | D1, interlace, rectangular pixel sensor              |

|  | 1500                       | 720                                  | 576                                | 25  | D1, interlace, rectangular pixel sensor              |

|  | 2000                       | 720                                  | 576                                | 25  | D1, interlace, rectangular pixel sensor              |

|  | 3000                       | 720                                  | 576                                | 25  | D1, interlace, rectangular pixel sensor              |

#### Table 1-2 H.264 Video Bitrates and Resolutions for PAL

#### 1.3.4 SVGA 800x600 Video Resolution

The MG1264 Codec supports a maximum video resolution of 800x600 (SVGA). This resolution is intended for playback on PCs. This SVGA mode is intended to work with the standard 27 MHz video clock. The maximum frame rate is 25 fps.

#### 1.3.5 Video Input and Output Scaling

The MG1264 Codec is capable of performing video scaling both on the input during pre-encoding and on the output during post-decoding. This allows the MG1264 Codec to use alternate video resolutions to facilitate display on standard televisions. It also facilitates applications that make use of lower resolutions such as streaming over low bandwidth networks.

#### Input Video Scaling

The Input Video Scaler is designed to take VGA/D1 resolution video input and generate the target encoding resolutions listed in Table 1-1. The MG1264 Codec supports a maximum horizontal resolution of 800pixels.

#### **Output Video Scaling**

The Output Video Scaler is designed to up-sample any resolution less than D1 for display on a standard television or down-sample for display on alternative displays. The Output Video Scaler also has the ability to perform square pixel to rectangular pixel conversion to support display of square pixel video correctly on a traditional TV display.

#### 1.3.6 User Control of H.264 Encoder Features (Tools)

The encoder features are selectable. Each feature has settings and/or ranges that affect the overall compression efficiency accordingly. This section shows the key features and their associated target settings.

#### Picture Resolution

Table 1-1 shows the video resolutions. This selection uses the Input Video Scaler to produce the desired resolution.

#### Video Frame Rate

The primary target for the MG1264 Codec is natural motion frame rate like that of NTSC video at 30 fps. The following alternate frame rates are also supported:

- 25 fps (for PAL applications)

- 15 fps

#### Video Bitrate

The target bitrates are listed in Table 1-1 for given resolutions. The maximum video data rate is 10 Mbps. The minimum video data rate is 300 kbps. The bitrate can be specified in 100 kbps increments from 300 kbps to 10 Mbps.

#### Picture Type

The Picture Type refers to as Frame or Field coding. Frame mode is the most common mode used in Digital Still Cameras because they have progressive sensors at 30 fps. Field mode is used in most other mobile devices. When Field mode is selected, all fields are encoded separately. The MG1264 Codec does not implement MBAFF mode.

#### **GOP Structure**

The MG1264 Codec uses I-frames and P-frames only. No B-frames. The GOP structure is user selectable. The default GOP length is 15.

#### 1.3.7 The AAC Audio CODEC

The MG1264 Codec can encode two-channel AAC audio encoding with 16-bit samples at sample rates of 22.05 kHz, 24 kHz, 32 kHz, 44.1 kHz, and 48 kHz. The target audio bitrate is 10% of the associated video bitrate, with an appropriate sample rate.

#### User Control of the AAC Encoder Features

The audio encoder features are selectable. Each feature has settings and/or ranges that affect the overall compression efficiency, accordingly. Table 1-3 shows the key features and their associated target settings.

| Feature Options |                                                |

|-----------------|------------------------------------------------|

| Channels        | Mono (1) or Stereo (2)                         |

| Sample rate     | 22.05 kHz, 24 kHz, 32 kHz, 44.1 kHz, or 48 kHz |

| Bitrate         | 8 kbps - 384 kbps                              |

#### Table 1-3 AAC Encoder Features

#### 1.3.8 I/O Control

The MG1264 Codec is intended to be a co-processor in a system with a basic architecture as shown in Figure 1-3. All system control is done by the System Host CPU, including booting and initializing the MG1264 Codec. All camera I/O functions are controlled by the system host processor. I/O functions include: LCD control, camera sensor control, TV output, mass storage controllers, USB, audio codec, etc.

### Chapter 2. MG1264 Codec Host Interface

The System Host CPU controls the MG1264 Low Power H.264 and AAC Codec for Mobile Devices through the MG1264 Codec Host Interface. The MG1264 Codec Host Interface also serves as the compressed data interface. This interface allows for directly-addressable access to the MG1264 Codec DRAM, the MG1264 Codec Bitstream write FIFO, and the MG1264 Codec registers.

#### 2.1 MG1264 Codec Host Interface Physical Description

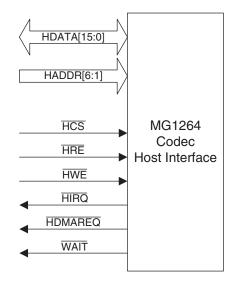

The MG1264 Codec Host Interface is modeled on the commonly used generic asynchronous-style interface. It consists of a 16-bit data path (HDATA[15:0], six bits of address (HADDR[6:1]), and control signals.

#### 2.1.1 Connection Diagram

The MG1264 Codec Host Interface connection diagram is shown in Figure 2-1.

Figure 2-1 MG1264 Codec Host Interface Connection Diagrams

The MG1264 Codec Host Interface has a single Host Chip Select and six address lines. All of the device's resources reside in a single address space, and the registers that can be addressed by the six address lines are shown in Table 2-2.

#### 2.1.2 MG1264 Codec Host Interface Signals

The signals that comprise the MG1264 Codec Host Interface are shown in Table 2-1.

| Table 2-1MG1264 Codec Host Interface Pin Descriptions |  |

|-------------------------------------------------------|--|

|-------------------------------------------------------|--|

| Pin Name    | Signal Name         | Direction                  | Description                                                                                                                                                                             |

|-------------|---------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HDATA[15:0] | Data [15:0]         | Bidirectional              | 16-bit Host Data Bus                                                                                                                                                                    |

| HADDR[6:1]  | Address [6:1]       | Inputs                     | Six bits of Host Address                                                                                                                                                                |

| HCS         | Host Chip<br>Select | Input                      | Active Low Host Chip Select. This chip select is<br>used to access the MG1264 Codec's Internal reg-<br>isters, External memory, bitstream read and write<br>FIFO registers.             |

| HRE         | RE                  | Input                      | Active Low Read Enable                                                                                                                                                                  |

| HWE         | WE                  | Input                      | Active Low Write Enable                                                                                                                                                                 |

| HIRQ        | ĪNT                 | Output<br>(Open Collector) | Active Low, Open Collector Host Interrupt Re-<br>quest                                                                                                                                  |

| HDMAREQ     | Host DMA Request    | Output                     | Bitstream DMA Request associated with the Bit-<br>stream port                                                                                                                           |

| HWAIT       | WAIT                | Output                     | Active low wait pin. The MG1264 Codec asserts<br>this pin to extend the bus cycle until it is able to ac-<br>cept data (during a write cycle) or present data<br>(during a read cycle). |

#### 2.2 MG1264 Codec Host Interface Logical Description

The MG1264 Codec Host Interface works in two completely different modes:

- System Control

- Compressed Data I/O Interface

These are discussed in the sections that follow.

#### 2.2.1 System Control

The MG1264 Codec is controlled through the MG1264 Codec Host Interface. When the MG1264 Codec is powered up, the System Host CPU must first download the firmware through the MG1264 Codec Host Interface, and then initialize the MG1264 Codec. The System Host CPU controls the operation of the MG1264 Codec by reading and writing specific registers inside the MG1264 Codec.

The MG1264 Codec is able to accept new commands or requests from the System Host CPU at least once every frame period. Control commands such as start/stop/pause are executed within one frame time of being issued.

#### 2.2.2 Compressed Data I/O Through the MG1264 Codec Host Interface

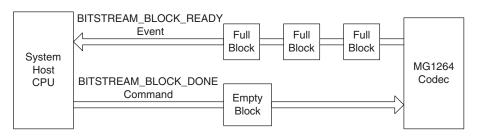

The MG1264 Codec Host Interface also transports compressed data in to (decoding) and out of (encoding) the MG1264 Codec. The System Host CPU can use Direct Memory Access (DMA) to facilitate these transfers.

#### 2.2.3 Interrupts

There is a single interrupt pin defined:  $\overline{\text{HIRQ}}$ . The MG1264 Codec has four interrupt sources that are logically OR'd together internally to form the  $\overline{\text{HIRQ}}$ :

- CSRInt: Configuration Status Register Interrupt

- EMInt: External Memory Interrupt

- BMInt: Bitstream Memory Interrupt

- MBint: Mailbox Interrupt

For information on the Interrupt Registers, refer to "Peripheral Interrupt Registers" on page 36.

#### 2.2.4 DMA Channels

The MG1264 Codec has two generic External Memory DMA engines. One is for System Host CPU access to the MG1264 Codec's DRAM including the mailbox. You can find information on this DMA interface in the section "External Memory Access Registers" on page 41.

The other is for Bitstream transfers. The Bitstream DMA is used for reading a bitstream from, and writing a bitstream to the Bitstream Write FIFO. You can also find information on this DMA interface in the section "Bitstream Write FIFO Access Registers" on page 47.

#### 2.2.5 Latency Considerations

Because internal operations such as DRAM and register access can incur a lot of latency, the MG1264 Codec's Host Interface uses an indirect access method to access the internal MG1264 Codec's processor resources. In this mode of operation, read and write accesses are deterministic and no Host Ready (or Wait) signaling is needed.

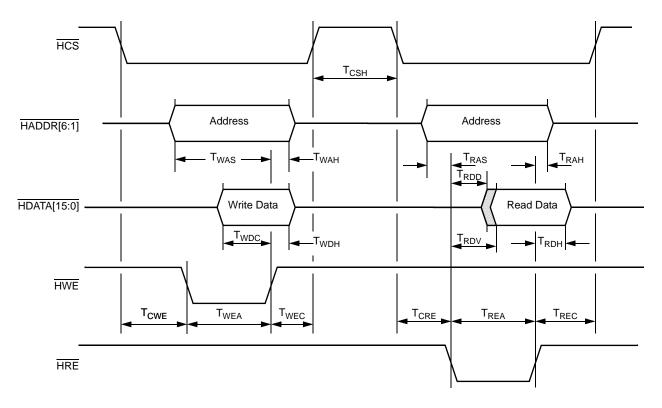

#### 2.3 Read/Write Timing

This section provides generic timing information for the MG1264 Codec Host Interface. For specific timing information, refer to "Specifications" on page 153. For information on the programming sequence needed to read or write a register, refer to "Register Definitions" on page 34.

The Read/Write control signals are programmable, and can be set to work in either Read Enable and Write Enable mode (default) or Read/Write and Enable mode. Note that these options are available in both single Host Chip Select mode and two Host Chip Select mode. Each of these modes is discussed in the sections that follow.

The MG1264 Codec defaults to the separate Read Enable and Write Enable signalling as shown in Figure 2-3 and Figure 2-4. To put the host interface into Read/Write and Enable mode (Figure 2-5 and Figure 2-6), the very first transaction on the read bus must be a Write transaction using the separate Enable and RD/WR signaling to register address 0x18. This register is not defined as a valid register and a write to it has no logical effect other than to put the chip into separate Enable and RD/WR mode. A data value of 0x0000 should be used.

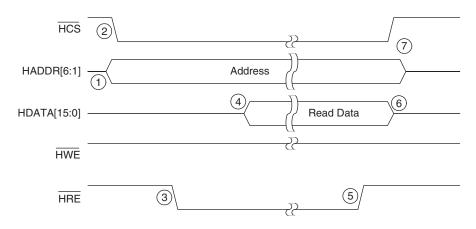

#### 2.3.1 Read Timing Sequence in Read Enable Mode

Figure 2-3 shows the timing for a System Host CPU read from the MG1264 Codec in Read Enable mode.

Figure 2-3 Read Access Timing in Read Enable Mode

- 1. The System Host CPU must assure that the address bus (HADDR[6:1]) is stable before asserting Host Chip Select (HCS).

- 2: The System Host CPU asserts the Host Chip Select signal to inform the MG1264 Codec that a read is in process. When Host Chip Select ( $\overline{HCS}$ ) is used, it accesses the MG1264 Codec's Internal registers and External memory.

- 3: The System Host CPU asserts the Host Read Enable (HRE) signal to inform the MG1264 Codec that the operation will be a read.

- 4: The data becomes available on HDATA[15:0].

- 5: Once the data has been taken, the System Host CPU de-asserts the Host Read Enable (HRE) signal to indicate to the MG1264 Codec that the transaction is complete.

- 6: The MG1264 Codec removes the output data from the data bus (HDATA[15:0]).

- 7: The System Host CPU then de-asserts the address bus (HADDR[6:1]) and the Host Chip Select to complete the transaction.

#### 2.3.2 Write Data Timing in Write Enable Mode

Figure 2-4 shows the timing for a System Host CPU write to the MG1264 Codec in Write Enable mode.

Figure 2-4 Write Access Timing in Write Enable Mode

- 1. The System Host CPU must assure that the address bus (HADDR[6:1]) and data to be written (on HDATA[15:0]) are stable before asserting the Host Chip Select (HCS).

- 2: The System Host CPU asserts the Host Chip Select signal to inform the MG1264 Codec that a write is in process. When the Host Chip Select (HCS) is used, it accesses the MG1264 Codec's Internal registers and External memory.

- 3: The System Host CPU asserts the Host Write Enable (HWE) signal to inform the MG1264 Codec that the operation will be a write.

- 4: The System Host CPU de-asserts the Host Write Enable (HWE) signal to indicate to the MG1264 Codec that the write is complete.

- 5: The System Host CPU de-asserts the Address bus (HADDR[6:1]), Write Data bus (HDATA[15:0]), and the Host Chip Select to indicate to the MG1264 Codec that the transaction is complete.

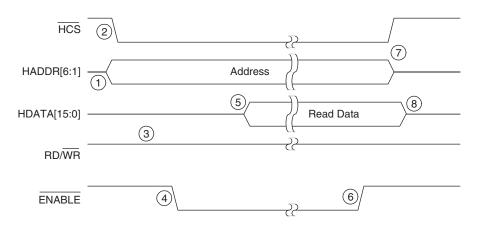

#### 2.3.3 Read Timing Sequence in Read/Write and Enable Mode

Figure 2-3 shows the timing for a System Host CPU read from the MG1264 Codec in Read/ Write mode.

Figure 2-5 Read Access Timing in Read/Write and Enable Mode

- 1. The System Host CPU must assure that the address bus (HADDR[6:1]) is stable before asserting Host Chip Select (HCS).

- 2: The System Host CPU asserts the Host Chip Select signal to inform the MG1264 Codec that a read is in process. When Host Chip Select (HCS) is used, it accesses the MG1264 Codec's Internal registers and External memory.

- 3: The System Host CPU sets the Read/Write signal high to inform the MG1264 Codec that the operation will be a read.

- 4: The System Host CPU asserts the Enable signal to start the read cycle.

- 5: The data becomes available on HDATA[15:0].

- 6: Once the data has been taken, the System Host CPU de-asserts the Enable signal to indicate to the MG1264 Codec that the transaction is complete.

- 7: The System Host CPU then de-asserts the address bus (HADDR[6:1]) and the Host Chip Select to complete the transaction.

- 8: The MG1264 Codec removes the output data from the data bus (HDATA[15:0]).

#### 2.3.4 Write Data Timing in Read/Write and Enable Mode

Figure 2-4 shows the timing for a System Host CPU write to the MG1264 Codec in Read/Write and Enable mode.

Figure 2-6 Write Access Timing in Read/Write and Enable Mode

- 1. The System Host CPU must assure that the address bus (HADDR[6:1]) and data to be written (on HDATA[15:0]) is stable before asserting the Host Chip Select (HCS).

- 2: The System Host CPU asserts the Host Chip Select signal to inform the MG1264 Codec that a write is in process. When the Host Chip Select (HCS) is used, it accesses the MG1264 Codec's Internal registers and External memory.

- 3: The System Host CPU sets the Read/Write signal (RD/WR) low to inform the MG1264 Codec that the operation will be a write.

- 4: The System Host CPU asserts the Enable signal to start the write cycle.

- 5: The System Host CPU de-asserts the Read/Write signal and Enable signal to indicate to the MG1264 Codec that the write is complete.

- 6: The System Host CPU de-asserts the Address bus (HADDR[6:1]), Write Data bus (HDATA[15:0]), and the Host Chip Select to indicate to the MG1264 Codec that the transaction is complete.

#### 2.4 DMA Transfers

The MG1264 Codec can be configured to do DMA transfers. When the MG1264 Codec is in DMA mode, the transfers on the external bus are a sequence of individual read and write transactions to a FIFO port mapped to a host interface register. See "Accessing External Memory Port 1 and Port 2" on page 39 for information on how to set up a DMA transfer.

When in DMA mode, the individual read or write transactions making up the DMA transactions must be paced. The MG1264 Codec signals the external host that it is ready to accept a read or write transaction. The pacing is accomplished using one of three mechanisms:

- The external HDMAREQ pin

- A register bit (EMFifoRdReq/ EMFifoWrReq)

- The external  $\overline{\text{HWAIT}}$  pin

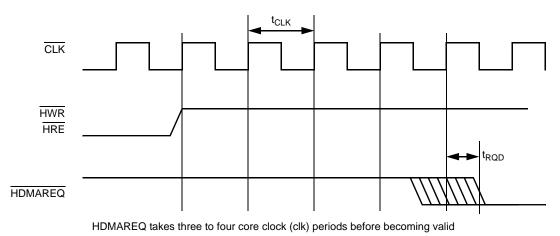

#### 2.4.1 Pacing using the HDMAREQ Pin

The MG1264 Codec asserts the HDMAREQ pin when a programmable threshold (EM-DThresh, see page 45) is reached in the DMA transfer FIFO. For a read DMA, the MG1264 Codec asserts the HDMAREQ pin when EMDThresh number of words is available to be transferred to the System Host CPU. The MG1264 Codec deasserts the HDMAREQ pin once the number of words available to be read falls below EMDThresh.

For a write DMA, the HDMAREQ pin is asserted when the MG1264 Codec is able to accept EMDThresh number of 1b-bit words to be written. The HDMAREQ pin is de-asserted once the number of words available to be written falls below EMDThresh.

#### 2.4.2 Pacing using the EMFifoRdReq/EMFifoWrReq Bits

The EMFifoRdReq or EMFifoWrReq Bits in the EMFifoStatus Register (see page 46) are reflections of the HDMARQ pin and are set accordingly if in read or write DMA mode.

#### 2.4.3 Pacing using the HWAIT Pin

Pacing using the HWAIT pin is slightly different than in HDMAREQ mode. In this case, the external host does not use the HDMAREQ or the EMFifoRdReq/EMFifoWrReq mechanisms. In the case of a read DMA transaction, the System Host CPU initiates read transactions without monitoring the HDMAREQ pin or the EMFifoRdReq bits. If the MG1264 Codec does not currently have data available for reading, it asserts the HWAIT signal during that individual read transaction until data is available. The transaction is not completed until HWAIT is deasserted.

In a write DMA transaction, the external host initiates write transactions without monitoring the  $\overline{\text{HDMAREQ}}$  pin or the EMFifoRdReq bits. If the MG1264 Codec is not currently able to accept write data, it asserts the  $\overline{\text{HWAIT}}$  signal during that individual write transaction until it is able to accept data. The transaction is not completed until  $\overline{\text{HWAIT}}$  is de-asserted.

#### 2.5 MG1264 Codec Register Indirect Access

The System Host CPU processor can only indirectly access the MG1264 Codec's internal Configuration and Status (CSR) registers and Mailbox registers (see Figure 2-2). This is done through a set of registers mapped to the Host Chip Select ( $\overline{HCS}$ ) over the MG1264 Codec Host Interface. These registers are not accessed during normal operation, and indirect addressing is typically only used by the bootloader.

#### 2.5.1 Reading a Register

The procedure to read an MG1264 Codec register is:

- 1. Before accessing a register, set up the PeriIntEn register to enable the Configuration or Status Register (CSR) interrupt, if that is the preferred method for getting the "Access Done" message. This only needs to be done once for all CSR accesses.

- 2: Write the Address to the CSRAddr register.

- 3: Write the Command bits (CSRAccess = 0) to the CSRCmd register.

- 4: Poll the CSRDone bit in the CSRStat register, or wait for the interrupt.

- 5: Read the return data from the CSRRdDataH and CSRRdDataL registers.

- 6: Read the CSRStat register and check that it has the expected value.

- 7: Clear the CSRInt bit in the PeriIntPend register, if using interrupts or clear the CSRDone bit in the CSRStatus register, if polling.

#### 2.5.2 Writing a Register

The procedure to write a MG1264 Codec register is:

- 1. Before accessing a register, set up the PeriIntEn register to enable the Configuration or Status Register (CSR) interrupt, if that is the preferred method for getting the "Access Done" message. This only needs to be done once for all CSR accesses.

- 2: Write the data to be written to the CSRWrDataH and CSRWrDataL registers.

- 3: Write the Address the CSRAddr register.

- 4: Write the Command bits (CSRAccess = 0) to the CSRCmd register.

- 5: Poll the CSRDone bit in the CSRStat register, or wait for the interrupt.

- 6: Read the CSRStat register and check that it has the expected value.

**Usage Note**: In some cases, it may be necessary to read CSRRdData to check a value returned by the internal processor if the operation is more complex than a simple register read or write.

7: Clear the CSRInt bit in the PeriIntPend register, if using interrupts or clear the CSRDone bit in the CSRStatus register, if polling.

#### 2.6 Programming the MG1264 Codec Host Interface

#### 2.6.1 Register Maps

Table 2-2 shows the MG1264 Codec Registers, External Memory Device Register Map, Bitstream Read Memory and Bitstream Write FIFO Device Register Map. These registers are addressed when the Host Chip Select ( $\overline{\text{HCS}}$ ) signal is asserted.

Table 2-2

MG1264 Codec Register and External Memory Device Register Map

| Register      | Offset | Access | Description                                                                                   | Page |

|---------------|--------|--------|-----------------------------------------------------------------------------------------------|------|

| CSRCmd        | 0x0020 | R/W    | Configuration/Status Register Command                                                         | 34   |

| CSRAddr       | 0x0022 | R/W    | Configuration/Status Register Address                                                         | 34   |

| CSRWrDataH    | 0x0024 | R/W    | Configuration/Status Register Write Data High                                                 | 34   |

| CSRWrDataL    | 0x0026 | R/W    | Configuration/Status Register Write Data Low                                                  | 34   |

| CSRRdDataH    | 0x0028 | Read   | Configuration/Status Register Read Data High                                                  | 35   |

| CSRRdDataL    | 0x002A | Read   | Configuration/Status Register Read Data Low                                                   | 35   |

| CSRStat       | 0x002C | R/W    | Configuration/Status Register Status                                                          | 35   |

| PeriIntPend   | 0x002E | R/W    | Peripherals Interrupt Pending                                                                 | 36   |

| PeriIntEnSet  | 0x0030 | R/W    | Peripherals Interrupt Enable - Set                                                            | 36   |

| PeriIntEnClr  | 0x0032 | R/W    | Peripherals Interrupt Enable - Clear                                                          | 36   |

| ClkConfig     | 0x0034 | R/W    | Clock Configuration Register                                                                  | 37   |

| PLL Dividers  | 0x0036 | R/W    | PLL Dividers Register                                                                         | 37   |

| ChipID        | 0x0038 | R      | Chip ID Register                                                                              | 38   |

| EM1Cmd        | 0x0000 | R/W    | External Memory DMA Command                                                                   | 41   |

| EM1XferSize   | 0x0002 | R/W    | External Memory DMA Transfer Size                                                             | 41   |

| EM1SrcAddrH   | 0x0004 | R/W    | External Memory DMA Source Address High or Starting Vertical/<br>Y Source Address             | 42   |

| EM1SrcAddrL   | 0x0006 | R/W    | External Memory DMA Source Address Low or Starting Horizon-<br>tal/X Source Address           | 42   |

| EM1DestAddrH  | 0x0008 | R/W    | External Memory DMA Destination Address High or Starting Ver-<br>tical/Y Destination Address  | 42   |

| EM1DestAddrL  | 0x000A | R/W    | External Memory DMA Destination Address Low or Starting Hor-<br>izontal/X Destination Address | 42   |

| EM1Status     | 0x000C | Read   | External Memory DMA Status                                                                    | 44   |

| EM1RemCount   | 0x000E | Read   | External Memory DMA Transfer Remainder Count                                                  | 44   |

| EM1Config     | 0x0010 | R/W    | External Memory DMA Configuration                                                             | 45   |

| EM1FifoRdPort | 0x0012 | Read   | External Memory DMA FIFO Read Port (from memory)                                              | 46   |

| Register      | Offset | Access | Description                                                                                 | Page |

|---------------|--------|--------|---------------------------------------------------------------------------------------------|------|

| EM1FifoWrPort | 0x0014 | R/W    | External Memory DMA FIFO Write Port (to memory)                                             | 46   |

| EM1FifoStatus | 0x0016 | Read   | Bitstream Memory DMA Status                                                                 | 46   |

| BFifoWrPort   | 0x0060 | R/W    | Bitstream FIFO Write Port (to Media Engine)                                                 | 47   |

| BFifoStatus   | 0x0062 | Read   | Bitstream FIFO Status Register                                                              | 47   |

| BFifoConfig   | 0x0064 | R/W    | Bitstream FIFO Command Register                                                             | 47   |

| EM2Cmd        | 0x0040 | R/W    | Bitstream Memory DMA Command                                                                | 41   |

| EM2XferSize   | 0x0042 | R/W    | Bitstream Memory DMA Transfer Size                                                          | 41   |

| EM2SrcAddrH   | 0x0044 | R/W    | Bitstream Memory DMA Source Address High<br>or Starting Vertical/Y Source Address           | 42   |

| EM2SrcAddrL   | 0x0046 | R/W    | Bitstream Memory DMA Source Address Low<br>or Starting Horizontal/X Source Address          | 42   |

| EM2DestAddrH  | 0x0048 | R/W    | Bitstream Memory DMA Destination Address High<br>or Starting Vertical/Y Destination Address | 42   |

| EM2DestAddrL  | 0x004A | R/W    | Bitstream Memory DMA Destination Address Low<br>or Starting Vertical/Y Source Address       | 42   |

| EM2Status     | 0x004C | Read   | Bitstream Memory DMA Status                                                                 | 44   |

| EM2RemCount   | 0x004E | Read   | Bitstream Memory DMA Transfer Remainder Count                                               | 44   |

| EM2Config     | 0x0050 | R/W    | Bitstream Memory DMA Configuration                                                          | 45   |

| EM2FifoRdPort | 0x0052 | Read   | Bitstream Memory DMA FIFO Read Port<br>(from memory)                                        | 46   |

| EM2FifoWrPort | 0x0054 | R/W    | Bitstream Memory DMA FIFO Write Port<br>(to memory)                                         | 46   |

| EM2FifoStatus | 0x0056 | Read   | Bitstream Memory DMA FIFO Status                                                            | 46   |

#### Table 2-2 MG1264 Codec Register and External Memory Device Register Map

#### 2.7 Register Definitions

#### 2.7.1 Configuration, Data, and Status Registers

#### Command/Status Register Command

| 15            | 14                                   | 13       | 12             | 11                                    | 10                  | 9        | 8        | 7        | 6       | 5       | 4                           | 3       | 2       | 1 | 0 |

|---------------|--------------------------------------|----------|----------------|---------------------------------------|---------------------|----------|----------|----------|---------|---------|-----------------------------|---------|---------|---|---|

| CSR<br>Access |                                      | CSRLen   | )              |                                       | Rese                | erved    |          | CSRE     | BlockID |         |                             |         |         |   |   |

| Reserve       | ed field                             | ls shoul | ld be ig       | nored (                               | maske               | d) whe   | n read   | , and o  | nly 0's | should  | l be wri                    | tten to | them.   |   |   |

| CSRAc         | cess                                 |          | CSRA<br>When   | ddr reg<br>a 1 is v                   | ister.<br>vritten 1 | o this f | ield. it | initiate | s a CS  | R write | from th<br>to the<br>/rData | addres  | ss prov |   |   |

| CSRLer        | ו                                    |          | 001 =<br>010 = | 4 byte<br>1 byte<br>2 byte<br>codes a | àccess<br>(halfwo   | rd) acc  | ess      | ould no  | t be us | ed.     |                             |         |         |   |   |

| CSRBlo        | bckID Block ID for a register access |          |                |                                       |                     |          |          |          |         |         |                             |         |         |   |   |

Command/Status Register Address

CSRAddr

CSRCmd

Offset: 0x0022

Offset: 0x0020

| 15   | 14  | 13 | 12                | 11 | 10 | 9 | 8   | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|------|-----|----|-------------------|----|----|---|-----|------|---|---|---|---|---|---|-------|

|      |     |    |                   |    |    |   | CSR | Addr |   |   |   |   |   |   |       |

| CSRA | ddr |    | Addres<br>[1:0] a |    |    |   |     |      |   |   |   |   |   |   | (bits |

Command/Status Register Write Data High CSRWrDataH

Offset: 0x0024

| 15   | 14      | 13 | 12               | 11 | 10                  | 9 | 8        | 7        | 6       | 5       | 4        | 3   | 2 | 1 | 0 |

|------|---------|----|------------------|----|---------------------|---|----------|----------|---------|---------|----------|-----|---|---|---|

|      |         |    |                  |    |                     |   | CSRW     | rDataH   |         |         |          |     |   |   |   |

| CSRW | /rDataF | 4  | High 1<br>Used v |    | egister f<br>SRWrDa |   | hich the | e data f | or a CS | SR writ | e is tak | en. |   |   |   |

Command/Status Register Write Data Low

CSRWrDataL

Offset: 0x0026

| 15   | 14      | 13 | 12               | 11 | 10 | 9 | 8        | 7       | 6       | 5        | 4         | 3   | 2 | 1 | 0 |

|------|---------|----|------------------|----|----|---|----------|---------|---------|----------|-----------|-----|---|---|---|

|      |         |    |                  |    |    |   | CSRW     | rDataL  |         |          |           |     |   |   |   |

| CSRW | VrDataL |    | Low 16<br>Used v |    |    |   | nich the | data fo | or a CS | SR write | e is take | en. |   |   |   |

|                                                                                                                                                                                                                                                                                                                                                                                           |          | Cor     | nmand            | /Statu               | s Regi               | ster Re                         | ad Da              | ta High           | 1                  | CSRF                  | RdData              | H                   | C                  | Offset:            | 0x0028             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|------------------|----------------------|----------------------|---------------------------------|--------------------|-------------------|--------------------|-----------------------|---------------------|---------------------|--------------------|--------------------|--------------------|

| 15                                                                                                                                                                                                                                                                                                                                                                                        | 14       | 13      | 12               | 11                   | 10                   | 9                               | 8                  | 7                 | 6                  | 5                     | 4                   | 3                   | 2                  | 1                  | 0                  |

|                                                                                                                                                                                                                                                                                                                                                                                           |          |         |                  |                      |                      |                                 |                    | dData⊢            | -                  |                       |                     |                     |                    |                    |                    |

| CSRF                                                                                                                                                                                                                                                                                                                                                                                      | RdData   | Η       | High 1<br>return | 6-bit re<br>ed for a | egister<br>a write.  | contain<br>Used \               | ing the<br>with CS | data re<br>RRdDa  | eturneo<br>ataL Th | d for a (<br>his regi | SR re<br>ster is    | ad or th<br>read-or | ne statu<br>nly.   | is infor           | mation             |

|                                                                                                                                                                                                                                                                                                                                                                                           |          | Cor     | nmand            | /Statu               | s Regi               | ster Re                         | ead Dat            | ta Low            |                    | CSRF                  | RdData              | L                   | С                  | Offset:            | 0x002A             |

| 15                                                                                                                                                                                                                                                                                                                                                                                        | 14       | 13      | 12               | 11                   | 10                   | 9                               | 8                  | 7                 | 6                  | 5                     | 4                   | 3                   | 2                  | 1                  | 0                  |

|                                                                                                                                                                                                                                                                                                                                                                                           |          |         |                  |                      |                      |                                 | CSRR               | dDataL            |                    |                       |                     |                     |                    |                    |                    |

| CSRF                                                                                                                                                                                                                                                                                                                                                                                      | RdData   | L       | Low 1<br>return  | 6-bit re<br>ed for a | gister o<br>a write. | containi<br>Used v              | ing the<br>with CS | data re<br>RRdDa  | eturned<br>ataH. T | l for a C<br>This reg | CSR read            | ad or th<br>read-c  | ne statu<br>only.  | is infor           | mation             |

| 45                                                                                                                                                                                                                                                                                                                                                                                        | 1 44     | 1       | mmand            | i                    | -                    |                                 | ł                  | -                 |                    | CSRS                  | ł                   | ·                   |                    | +                  | 0x0020             |