MPC506A MPC507A

SBFS018A - JANUARY 1988 - REVISED OCTOBER 2003

# Single-Ended 16-Channel/Differential 8-Channel CMOS ANALOG MULTIPLEXERS

## FEATURES

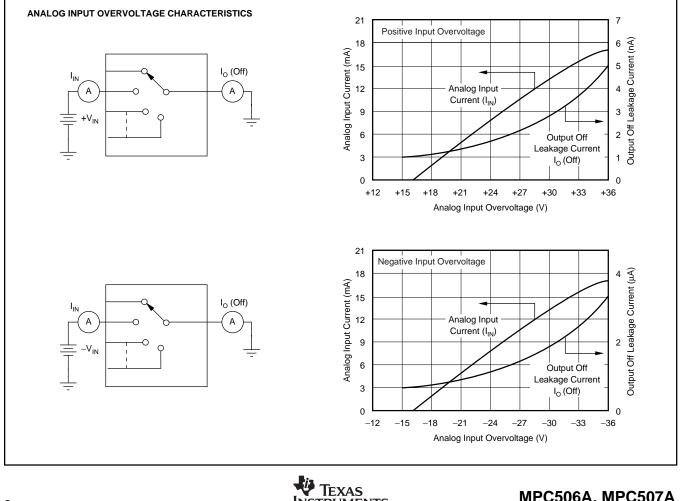

- ANALOG OVERVOLTAGE PROTECTION: 70V<sub>PP</sub>

- NO CHANNEL INTERACTION DURING OVERVOLTAGE

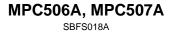

- BREAK-BEFORE-MAKE SWITCHING

- ANALOG SIGNAL RANGE: ±15V

- STANDBY POWER: 7.5mW typ

- TRUE SECOND SOURCE

## DESCRIPTION

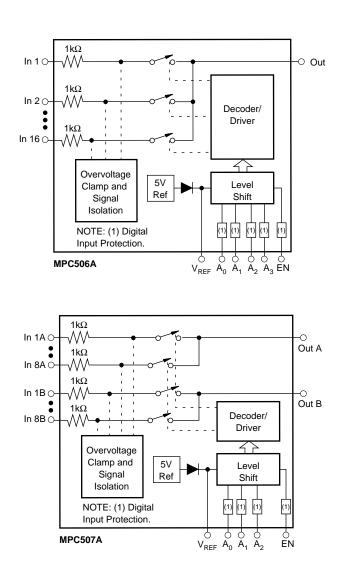

The MPC506A is a 16-channel single-ended analog multiplexer, and the MPC507A is an 8-channel differential multiplexer.

The MPC506A and MPC507A multiplexers have input overvoltage protection. Analog input voltages may exceed either power supply voltage without damaging the device or disturbing the signal path of other channels. The protection circuitry assures that signal fidelity is maintained even under fault conditions that would destroy other multiplexers. Analog inputs can withstand 70V<sub>PP</sub> signal levels and standard ESD tests. Signal sources are protected from short circuits should multiplexer power loss occur; each input presents a 1k $\Omega$ resistance under this condition. Digital inputs can also sustain continuous faults up to 4V greater than either supply voltage.

These features make the MPC506A and MPC507A ideal for use in systems where the analog signals originate from external equipment or separately powered sources.

The MPC506A and MPC507A are fabricated with Burr-Brown's dielectrically isolated CMOS technology. The multiplexers are available in plastic DIP and plastic SOIC packages. Temperature range is  $-40/+85^{\circ}$ C.

## FUNCTIONAL DIAGRAMS

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

# **ELECTRICAL CHARACTERISTICS**

Supplies = +15V, -15V;  $V_{REF}$  (Pin 13) = Open;  $V_{AH}$  (Logic Level High) = +4.0V;  $V_{AL}$  (Logic Level Low) = +0.8V unless otherwise specified.

|                                                                     |       |     | MPC506A/MPC507A |     |       |  |  |

|---------------------------------------------------------------------|-------|-----|-----------------|-----|-------|--|--|

| PARAMETER                                                           | TEMP  | MIN | MIN TYP         |     | UNITS |  |  |

| ANALOG CHANNEL CHARACTERISTICS                                      |       |     |                 |     |       |  |  |

| V <sub>s</sub> , Analog Signal Range                                | Full  | -15 |                 | +15 | V     |  |  |

| R <sub>ov</sub> , On Resistance <sup>(1)</sup>                      | +25°C |     | 1.3             | 1.5 | kΩ    |  |  |

| ON?                                                                 | Full  |     | 1.5             | 1.8 | kΩ    |  |  |

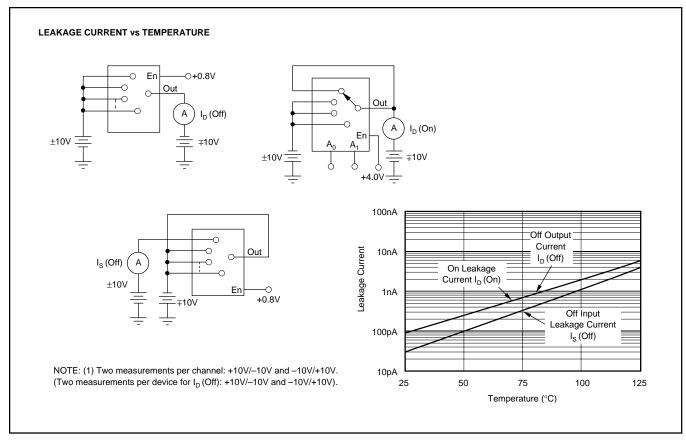

| Is (OFF), Off Input Leakage Current                                 | +25°C |     | 0.5             |     | nA    |  |  |

| 3 ( )                                                               | Full  |     |                 | 10  | nA    |  |  |

| I <sub>D</sub> (OFF), Off Output Leakage Current                    | +25°C |     | 0.2             | -   | nA    |  |  |

| MPC506A                                                             | Full  |     |                 | 5   | nA    |  |  |

| MPC507A                                                             | Full  |     |                 | 5   | nA    |  |  |

| I <sub>D</sub> (OFF) with Input Overvoltage Applied <sup>(2)</sup>  | +25°C |     | 2               | -   | μA    |  |  |

| I <sub>D</sub> (ON), On Channel Leakage Current                     | +25°C |     | 2               |     | nA    |  |  |

| MPC506A                                                             | Full  |     |                 | 10  | nA    |  |  |

| MPC507A                                                             | Full  |     |                 | 10  | nA    |  |  |

| I <sub>DIFF</sub> Differential Off Output Leakage Current           |       |     |                 |     |       |  |  |

| (MPC507A Only)                                                      | Full  |     |                 | 10  | nA    |  |  |

| DIGITAL INPUT CHARACTERISTICS                                       |       |     |                 |     |       |  |  |

| V <sub>AI</sub> , Input Low Threshold                               | Full  |     |                 | 0.8 | V     |  |  |

| V <sub>AH</sub> , Input High Threshold <sup>(3)</sup>               | Full  | 4.0 |                 |     | V     |  |  |

| V <sub>AL</sub> , MOS Drive <sup>(4)</sup>                          | +25°C |     |                 | 0.8 | V     |  |  |

| V <sub>AH</sub> , MOS Drive <sup>(4)</sup>                          | +25°C | 6.0 |                 |     | V     |  |  |

| I <sub>A</sub> , Input Leakage Current (High or Low) <sup>(5)</sup> | Full  |     |                 | 1.0 | μΑ    |  |  |

| SWITCHING CHARACTERISTICS                                           |       |     |                 |     |       |  |  |

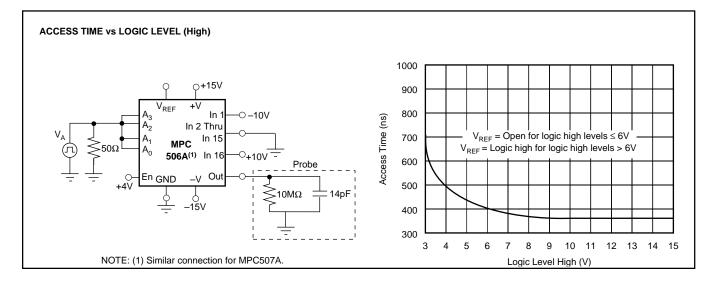

| t₄, Access Time                                                     | +25°C |     | 0.3             |     | μs    |  |  |

|                                                                     | Full  |     |                 | 0.6 | μs    |  |  |

| t <sub>open</sub> , Break-Before-Make Delay                         | +25°C | 25  | 80              |     | ns    |  |  |

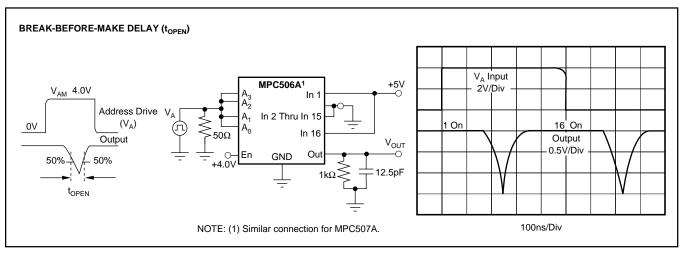

| (EN), Enable Delay (ON)                                             | +25°C |     | 200             |     | ns    |  |  |

|                                                                     | Full  |     |                 | 500 | ns    |  |  |

| toFF (EN), Enable Delay (OFF)                                       | +25°C |     | 250             |     | ns    |  |  |

|                                                                     | Full  |     |                 | 500 | ns    |  |  |

| Settling Time (0.1%)                                                | +25°C |     | 1.2             |     | μs    |  |  |

| (0.01%)                                                             | +25°C |     | 3.5             |     | μs    |  |  |

| "OFF Isolation" <sup>(6)</sup>                                      | +25°C | 50  | 68              |     | dB    |  |  |

| C <sub>s</sub> (OFF), Channel Input Capacitance                     | +25°C |     | 5               |     | pF    |  |  |

| $C_{\rm D}$ (OFF), Channel Output Capacitance: MPC506A              | +25°C |     | 50              |     | pF    |  |  |

| MPC507A                                                             | +25°C |     | 25              |     | pF    |  |  |

| C <sub>4</sub> , Digital Input Capacitance                          | 25°C  |     | 5               |     | pF    |  |  |

| C <sub>DS</sub> , (OFF), Input to Output Capacitance                | +25°C |     | 0.1             |     | pF    |  |  |

| POWER REQUIREMENTS                                                  |       |     |                 |     |       |  |  |

| P <sub>D</sub> , Power Dissipation                                  | Full  |     | 7.5             |     | mW    |  |  |

| I+, Current Pin 1 <sup>(7)</sup>                                    | Full  |     | 0.7             | 1.5 | mA    |  |  |

| I–, Current Pin 27 <sup>(7)</sup>                                   | Full  |     | 5               | 20  | μΑ    |  |  |

NOTES: (1)  $V_{OUT} = \pm 10V$ ,  $I_{OUT} = -100\mu$ A. (2) Analog overvoltage =  $\pm 33V$ . (3) To drive from DTL/TTL circuits. 1k $\Omega$  pull-up resistors to +5.0V supply are recommended. (4)  $V_{REF} = +10V$ . (5) Digital input leakage is primarily due to the clamp diodes. Typical leakage is less than 1nA at 25°C. (6)  $V_{EN} = 0.8V$ ,  $R_{L} = 1k\Omega$ ,  $C_{L} = 15pF$ ,  $V_{S} = 7Vrms$ , f = 100kHz. Worst-case isolation occurs on channel 8 due to proximity of the output pins. (7)  $V_{EN}$ ,  $V_{A} = 0V$  or 4.0V.

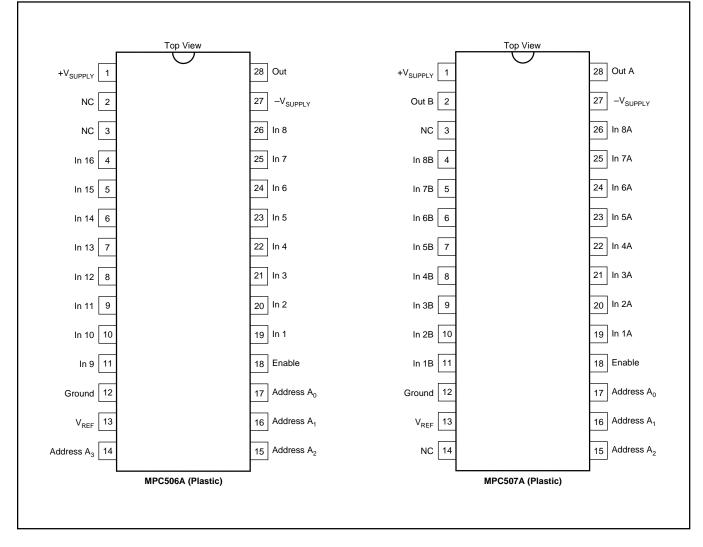

## **PIN CONFIGURATION**

## **TRUTH TABLES**

#### MPC506A

| A <sub>3</sub> | A <sub>2</sub> | <b>A</b> <sub>1</sub> | A <sub>0</sub> | EN | "ON"<br>CHANNEL |

|----------------|----------------|-----------------------|----------------|----|-----------------|

| Х              | Х              | х                     | х              | L  | None            |

| L              | L              | L                     | L              | н  | 1               |

| L              | L              | L                     | н              | н  | 2               |

| L              | L              | н                     | L              | н  | 3               |

| L              | L              | н                     | н              | н  | 4               |

| L              | Н              | L                     | L              | н  | 5               |

| L              | Н              | L                     | н              | н  | 6               |

| L              | Н              | н                     | L              | н  | 7               |

| L              | Н              | н                     | н              | н  | 8               |

| н              | L              | L                     | L              | н  | 9               |

| н              | L              | L                     | Н              | н  | 10              |

| н              | L              | н                     | L              | н  | 11              |

| н              | L              | н                     | Н              | н  | 12              |

| н              | Н              | L                     | L              | н  | 13              |

| н              | Н              | L                     | Н              | н  | 14              |

| н              | Н              | Н                     | L              | н  | 15              |

| н              | н              | Н                     | Н              | н  | 16              |

#### MPC507A

| A <sub>2</sub> | A <sub>1</sub> | A <sub>o</sub> | EN | "ON"<br>CHANNEL<br>PAIR |

|----------------|----------------|----------------|----|-------------------------|

| Х              | Х              | Х              | L  | None                    |

| L              | L              | L              | н  | 1                       |

| L              | L              | н              | н  | 2                       |

| L              | н              | L              | н  | 3                       |

| L              | н              | н              | н  | 4                       |

| н              | L              | L              | н  | 5                       |

| н              | L              | н              | н  | 6                       |

| н              | н              | L              | н  | 7                       |

| н              | н              | Н              | н  | 8                       |

## ABSOLUTE MAXIMUM RATINGS(1)

| Voltage between supply pins 44V                                             |

|-----------------------------------------------------------------------------|

| V <sub>REF</sub> to ground, V+ to ground22V                                 |

| V- to ground 25V                                                            |

| Digital input overvoltage:                                                  |

| V <sub>EN</sub> , V <sub>A</sub> : V <sub>SUPPLY</sub> (+)                  |

| V <sub>SUPPLY</sub> (-)4V                                                   |

| or 20mA, whichever occurs first.                                            |

| Analog input overvoltage:                                                   |

| V <sub>s</sub> : V <sub>SUPPLY</sub> (+)                                    |

| V <sub>SUPPLY</sub> (–)–20V                                                 |

| Continuous current, S or D                                                  |

| Peak current, S or D                                                        |

| (pulsed at 1ms, 10% duty cycle max) 40mA                                    |

| Power dissipation* 2.0W                                                     |

| Operating temperature range40°C to +85°C                                    |

| Storage temperature range65°C to +150°C                                     |

|                                                                             |

| *Derate 20.0mW/°C above T <sub>A</sub> = 70                                 |

| NOTE: (1) Absolute maximum ratings are limiting values, applied individu-   |

| ally, beyond which the serviceability of the circuit may be impaired. Func- |

| tional operation under any of these conditions is not necessarily implied.  |

|                                                                             |

### PACKAGE/ORDERING INFORMATION

For the most current package and ordering information, see the Package Option Addendum located at the end of this data sheet.

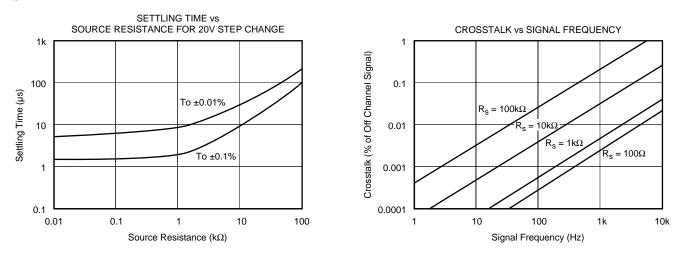

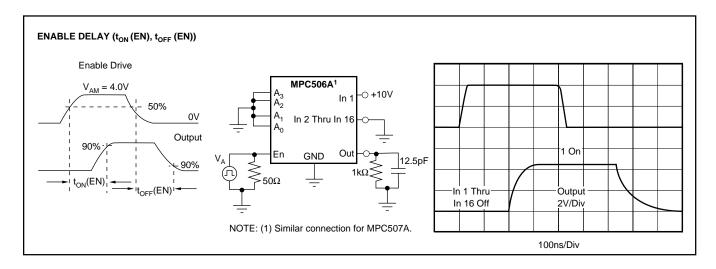

## **TYPICAL PERFORMANCE CURVES**

$T_{A} = +25^{\circ}C$  unless otherwise noted.

www.ti.com

## DISCUSSION OF SPECIFICATIONS

## **DC CHARACTERISTICS**

The static or dc transfer accuracy of transmitting the multiplexer input voltage to the output depends on the channel ON resistance ( $R_{ON}$ ), the load impedance, the source impedance, the load bias current and the multiplexer leakage current.

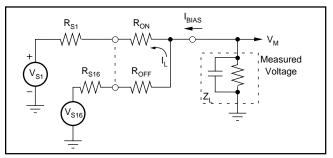

#### Single-Ended Multiplexer Static Accuracy

The major contributors to static transfer accuracy for singleended multiplexers are:

Source resistance loading error Multiplexer ON resistance error dc offset error caused by both load bias current and multiplexer leakage current.

Resistive Loading Errors

The source and load impedances will determine the input resistive loading errors. To minimize these errors:

- Keep loading impedance as high as possible. This minimizes the resistive loading effects of the source resistance and multiplexer ON resistance. As a guideline, load impedance of 10<sup>8</sup>Ω or greater will keep resistive loading errors to 0.002% or less for 1000Ω source impedances. A 10<sup>6</sup>Ω load impedance will increase source loading error to 0.2% or more.

- Use sources with impedances as low as possible. A  $1000\Omega$  source resistance will present less than 0.001% loading error and  $10k\Omega$  source resistance will increase source loading error to 0.01% with a  $10^8$  load impedance.

Input resistive loading errors are determined by the following relationship (see Figure 1).

FIGURE 1. MPC506A Static Accuracy Equivalent Circuit.

Source and Multiplexer Resistive Loading Error

$$\in (\mathsf{R}_{\mathsf{S}} + \mathsf{R}_{\mathsf{ON}}) = \frac{\mathsf{R}_{\mathsf{S}} + \mathsf{R}_{\mathsf{ON}}}{\mathsf{R}_{\mathsf{S}} + \mathsf{R}_{\mathsf{ON}} + \mathsf{R}_{\mathsf{L}}} \times 100$$

where  $R_s$  = source resistance

$R_L = load resistance$

$R_{ON}$  = multiplexer ON resistance

### Input Offset Voltage

Bias current generates an input OFFSET voltage as a result of the IR drop across the multiplexer ON resistance and source resistance. A load bias current of 10nA will generate an offset voltage of  $20\mu$ V if a 1k $\Omega$  source is used. In general, for the MPC506A, the OFFSET voltage at the output is determined by:

$$V_{\text{OFFSET}} = (I_{\text{B}} + I_{\text{L}}) (R_{\text{ON}} + R_{\text{S}})$$

where  $I_B = Bias$  current of device multiplexer is driving

$I_L = Multiplexer leakage current$

$R_{ON} = Multiplexer ON resistance$

$R_s =$ Source resistance

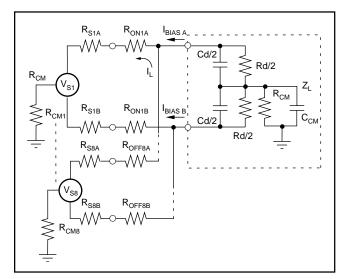

#### **Differential Multiplexer Static Accuracy**

Static accuracy errors in a differential multiplexer are difficult to control, especially when it is used for multiplexing low-level signals with full-scale ranges of 10mV to 100mV.

The matching properties of the multiplexer, source and output load play a very important part in determining the transfer accuracy of the multiplexer. The source impedance unbalance, common-mode impedance, load bias current mismatch, load differential impedance mismatch, and common-mode impedance of the load all contribute errors to the multiplexer. The multiplexer ON resistance mismatch, leakage current mismatch and ON resistance also contribute to differential errors.

Referring to Figure 2, the effects of these errors can be minimized by following the general guidelines described in this section, especially for low-level multiplexing applications.

FIGURE 2. MPC507A Static Accuracy Equivalent Circuit.

MPC506A, MPC507A SBFS018A

### Load (Output Device) Characteristics

- Use devices with very low bias current. Generally, FET input amplifiers should be used for low-level signals less than 50mV FSR. Low bias current bipolar input amplifiers are acceptable for signal ranges higher than 50mV FSR. Bias current matching will determine the input offset.

- The system dc common-mode rejection (CMR) can never be better than the combined CMR of the multiplexer and driven load. System CMR will be less than the device which has the lower CMR figure.

- Load impedances, differential and common-mode, should be  $10^{10}\Omega$  or higher.

### SOURCE CHARACTERISTICS

- The source impedance unbalance will produce offset, common-mode and channel-to-channel gain-scatter errors. Use sources which do not have large impedance unbalances if at all possible.

- Keep source impedances as low as possible to minimize resistive loading errors.

- Minimize ground loops. If signal lines are shielded, ground all shields to a common point at the system analog common.

If the MPC507A is used for multiplexing high-level signals of 1V to 10V full-scale ranges, the foregoing precautions should still be taken, but the parameters are not as critical as for low-level signal applications.

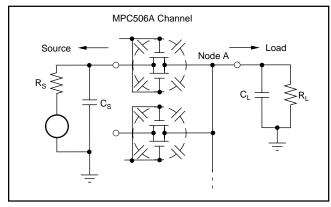

### **DYNAMIC CHARACTERISTICS**

#### Settling Time

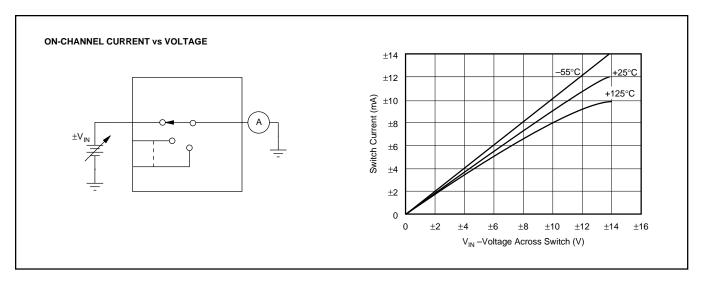

The gate-to-source and gate-to-drain capacitance of the CMOS FET switches, the RC time constants of the source and the load determine the settling time of the multiplexer.

Governed by the charge transfer relation i = C (dV/dt), the charge currents transferred to both load and source by the analog switches are determined by the amplitude and rise time of the signal driving the CMOS FET switches and the gate-to-drain and gate-to-source junction capacitances as shown in Figures 3 and 4. Using this relationship, one can

FIGURE 3. Settling Time Effects-MPC506A.

see that the amplitude of the switching transients seen at the source and load decrease proportionally as the capacitance of the load and source increase. The trade-off for reduced switching transient amplitude is increased settling time. In effect, the amplitude of the transients seen at the source and load are:

$$dV_{L} = (i/C) dt$$

where i = C (dV/dt) of the CMOS FET switches

C = load or source capacitance

The source must then redistribute this charge, and the effect of source resistance on settling time is shown in the Typical Performance Curves. This graph shows the settling time for a 20V step change on the input. The settling time for smaller step changes on the input will be less than that shown in the curve.

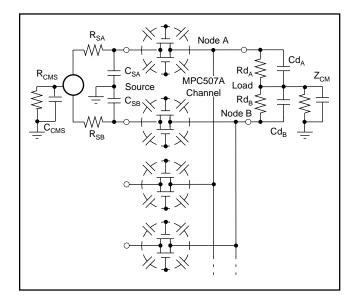

FIGURE 4. Settling and Common-Mode Effects— MPC507A

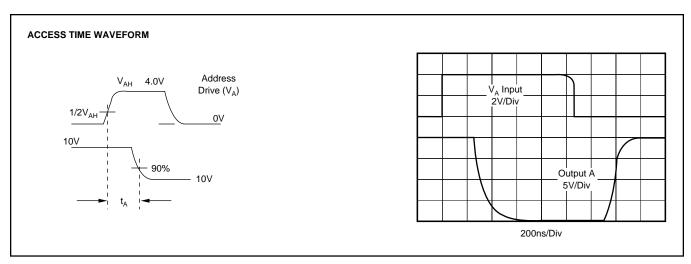

#### Switching Time

This is the time required for the CMOS FET to turn ON after a new digital code has been applied to the Channel Address inputs. It is measured from the 50 percent point of the address input signal to the 90 percent point of the analog signal seen at the output for a 10V signal change between channels.

#### Crosstalk

Crosstalk is the amount of signal feedthrough from the seven (MPC507A) or 15 (MPC506A) OFF channels appearing at the multiplexer output. Crosstalk is caused by the voltage divider effect of the OFF channel, OFF resistance and junction capacitances in series with the  $R_{ON}$  and  $R_s$  impedances of the ON channel. Crosstalk is measured with a 20Vp-p 1000Hz sine wave applied to all off channels. The crosstalk for these multiplexers is shown in the Typical Performance Curves.

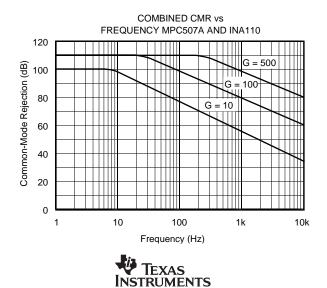

#### Common-Mode Rejection (MPC507A Only)

The matching properties of the load, multiplexer and source affect the common-mode rejection (CMR) capability of a differentially multiplexed system. CMR is the ability of the multiplexer and input amplifier to reject signals that are common to both inputs, and to pass on only the signal difference to the output. For the MPC507A, protection is provided for common-mode signals of  $\pm 20V$  above the power supply voltages with no damage to the analog switches.

The CMR of the MPC507A and Burr-Brown's INA110 instrumentation amplifier (G = 100) is 110dB at DC to 10Hz with a 6dB/octave roll-off to 70dB at 1000Hz. This measurement of CMR is shown in the Typical Performance Curves and is made with a Burr-Brown INA110 instrumentation amplifier connected for gains of 500, 100, and 10.

Factors which will degrade multiplexer and system DC CMR are:

- Amplifier bias current and differential impedance mismatch

- Load impedance mismatch

- Multiplexer impedance and leakage current mismatch

- Load and source common-mode impedance

AC CMR roll-off is determined by the amount of commonmode capacitances (absolute and mismatch) from each signal line to ground. Larger capacitances will limit CMR at higher frequencies; thus, if good CMR is desired at higher frequencies, the common-mode capacitances and unbalance of signal lines and multiplexer to amplifier wiring must be minimized. Use twisted-shielded pair signal lines wherever possible.

#### SWITCHING WAVEFORMS

Typical at +25°C, unless otherwise noted

## PERFORMANCE CHARACTERISTICS AND TEST CIRCUITS

$T_{_{A}} = +25^{\circ}C, V_{_{S}} = \pm 15V, V_{_{AM}} = +4V, V_{_{AL}} = 0.8V \text{ and } V_{_{REF}} = \text{Open, unless otherwise noted.}$

INSTRUMENTS

www.ti.com

## PERFORMANCE CHARACTERISTICS AND TEST CIRCUITS (CONT)

$\rm T_{_A} = +25^{\circ}C, \ V_{_S} = \pm 15V, \ \ V_{_{AM}} = +4V, \ \ V_{_{AL}} = 0.8V \ and \ \ V_{_{REF}} = Open, \ unless \ otherwise \ noted.$

## PERFORMANCE CHARACTERISTICS AND TEST CIRCUITS (CONT)

$T_{_A} = +25^{\circ}C, V_{_S} = \pm 15V, V_{_{AM}} = +4V, V_{_{AL}} = 0.8V \text{ and } V_{_{REF}} = \text{Open, unless otherwise noted}.$

## INSTALLATION AND OPERATING INSTRUCTIONS

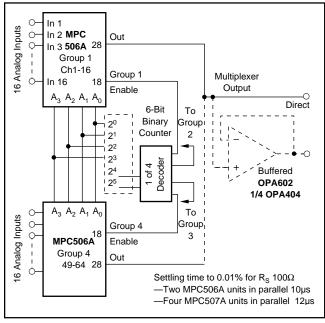

The ENABLE input, pin 18, is included for expansion of the number of channels on a single node as illustrated in Figure 5. With ENABLE line at a logic 1, the channel is selected by the 3-bit (MPC507A or 4-bit MPC506A) Channel Select Address (shown in the Truth Tables). If ENABLE is at logic 0, all channels are turned OFF, even if the Channel Address Lines are active. If the ENABLE line is not to be used, simply tie it to +V supply.

If the +15V and/or -15V supply voltage is absent or shorted to ground, the MPC507A and MPC506A multiplexers will not be damaged; however, some signal feedthrough to the output will occur. Total package power dissipation must not be exceeded.

For best settling speed, the input wiring and interconnections between multiplexer output and driven devices should be kept as short as possible. When driving the digital inputs from TTL, open collector output with pull up resistors are recommended (see Typical Performance Curves, Access Time).

To preserve common-mode rejection of the MPC507A, use twisted-shielded pair wire for signal lines and inter-tier connections and/or multiplexer output lines. This will help common-mode capacitance balance and reduce stray signal pickup. If shields are used, all shields should be connected as close as possible to system analog common or to the common-mode guard driver.

FIGURE 5. 64-Channel, Single-Tier Expansion.

## CHANNEL EXPANSION

### Single-Ended Multiplexer (MPC506A)

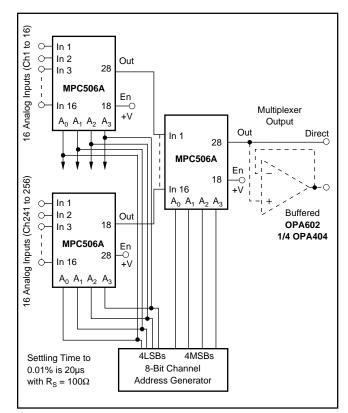

Up to 64 channels (four multiplexers) can be connected to a single node, or up to 256 channels using 17 MPC506A multiplexers on a two-tiered structure as shown in Figures 5 and 6.

## **MPC506A, MPC507A**

## **Differential Multiplexer (MPC507A)**

Single or multitiered configurations can be used to expand multiplexer channel capacity up to 64 channels using a  $64 \times 1$  or an  $8 \times 8$  configuration.

## Single-Node Expansion

The 64 x 1 configuration is simply eight (MPC507A) units tied to a single node. Programming is accomplished with a 6-bit counter, using the 3LSBs of the counter to control Channel Address inputs  $A_0$ ,  $A_1$ ,  $A_2$  and the 3MSBs of the counter to drive a 1-of-8 decoder. The 1-of-8 decoder then is used to drive the ENABLE inputs (pin 18) of the MPC507A multiplexers.

## **Two-Tier Expansion**

Using an 8 x 8 two-tier structure for expansion to 64 channels, the programming is simplified. The 6-bit counter output does not require a 1-of-8 decoder. The 3LSBs of the counter drive the  $A_0$ ,  $A_1$  and  $A_2$  inputs of the eight first-tier multiplexers and the 3MSBs of the counter are applied to the  $A_0$ ,  $A_1$ , and  $A_2$  inputs of the second-tier multiplexer.

### Single vs Multitiered Channel Expansion

In addition to reducing programming complexity, two-tier configuration offers the added advantages over single-node expansion of reduced OFF channel current leakage (reduced OFFSET), better CMR, and a more reliable configuration if a channel should fail ON in the single-node configuration, data cannot be taken from any channel, whereas only one channel group is failed (8 or 16) in the multitiered configuration.

FIGURE 6. Channel Expansion up to 256 Channels Using 16x16 Two-Tiered Expansion

TEXAS INSTRUMENTS

16-Feb-2009

## **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Packag<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|---------------|---------------------------|------------------|------------------------------|

| MPC506AP         | ACTIVE                | PDIP            | NTD                | 28   | 13            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| MPC506APG4       | ACTIVE                | PDIP            | NTD                | 28   | 13            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| MPC506AU         | ACTIVE                | SOIC            | DW                 | 28   | 20            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| MPC506AU/1K      | ACTIVE                | SOIC            | DW                 | 28   | 1000          | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| MPC506AU/1KG4    | ACTIVE                | SOIC            | DW                 | 28   | 1000          | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| MPC506AUG4       | ACTIVE                | SOIC            | DW                 | 28   | 20            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| MPC507AP         | ACTIVE                | PDIP            | NTD                | 28   | 13            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| MPC507APG4       | ACTIVE                | PDIP            | NTD                | 28   | 13            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type           |

| MPC507AU         | ACTIVE                | SOIC            | DW                 | 28   | 20            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| MPC507AU/1K      | ACTIVE                | SOIC            | DW                 | 28   | 1000          | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| MPC507AU/1KG4    | ACTIVE                | SOIC            | DW                 | 28   | 1000          | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAF          |

| MPC507AUG4       | ACTIVE                | SOIC            | DW                 | 28   | 20            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAF          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

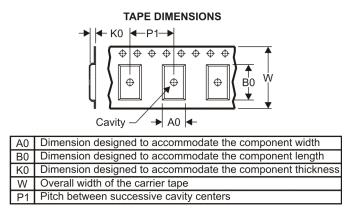

## TAPE AND REEL INFORMATION

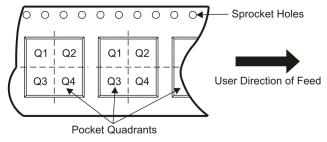

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |      |                    |    |      |                          |                          |         |         |         |            |           |                  |

|-----------------------------|------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| Device                      |      | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| MPC506AU/1K                 | SOIC | DW                 | 28 | 1000 | 330.0                    | 32.4                     | 11.35   | 18.67   | 3.1     | 16.0       | 32.0      | Q1               |

| MPC507AU/1K                 | SOIC | DW                 | 28 | 1000 | 330.0                    | 32.4                     | 11.35   | 18.67   | 3.1     | 16.0       | 32.0      | Q1               |

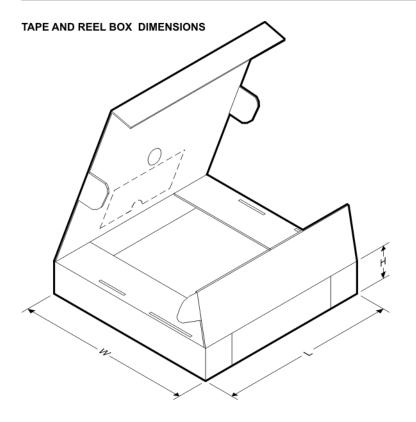

## PACKAGE MATERIALS INFORMATION

11-Mar-2008

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| MPC506AU/1K | SOIC         | DW              | 28   | 1000 | 346.0       | 346.0      | 49.0        |

| MPC507AU/1K | SOIC         | DW              | 28   | 1000 | 346.0       | 346.0      | 49.0        |

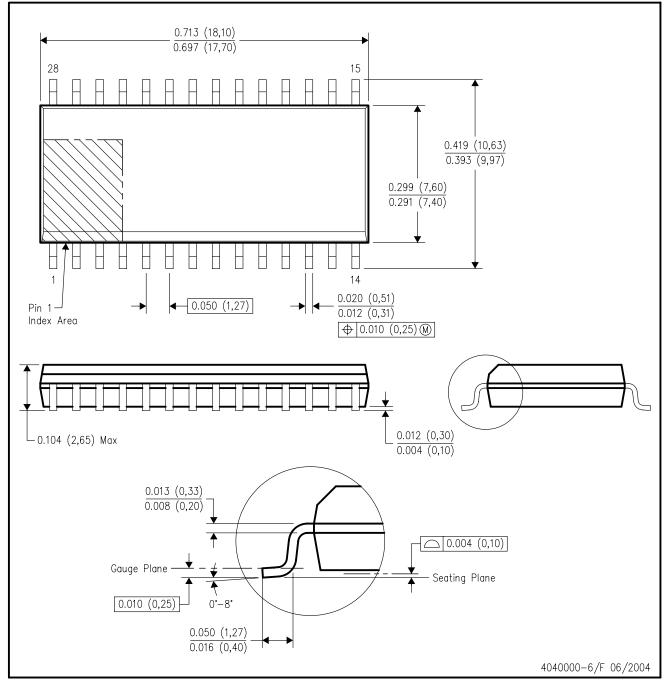

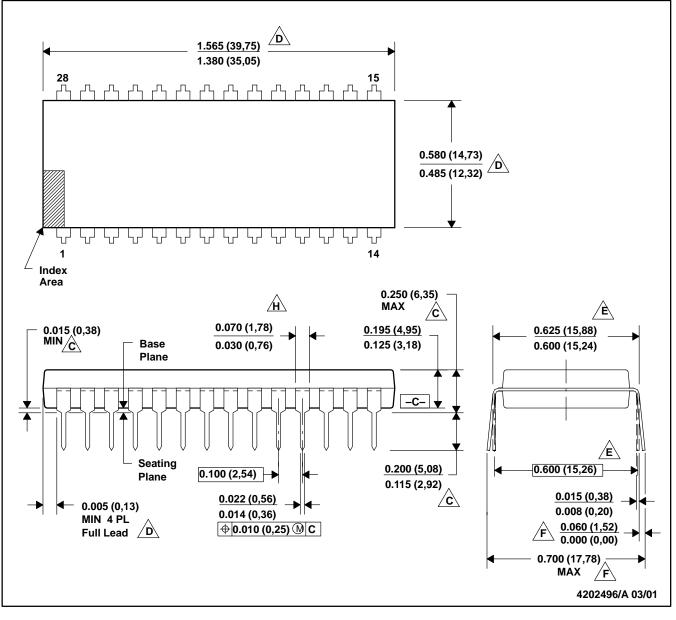

DW (R-PDSO-G28)

PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-013 variation AE.

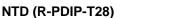

## **MECHANICAL DATA**

MPDI056 - APRIL 2001

PLASTIC DUAL-IN-LINE

- NOTES: A. All linear dimensions are in inches (millimeters). B. This drawing is subject to change without notice.

- Dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 (0,25). Dimensions measured with the leads constrained to be

- perpendicular to Datum C.

- F Dimensions are measured at the lead tips with the leads unconstrained.

- G. Pointed or rounded lead tips are preferred to ease  $\wedge$  insertion.

- <u>A.</u> Maximum dimension does not include dambar protrusions. Dambar protrusions shall not exceed 0.010 (0,25).

- I. Distance between leads including dambar protrusions to be 0.005 (0,13) minumum.

- J. A visual index feature must be located within the cross-hatched area.

- K. For automatic insertion, any raised irregularity on the top surface (step, mesa, etc.) shall be symmetrical about the lateral and longitudinal package centerlines.

- L. Controlling dimension in inches. M. Falls within JEDEC MS-011-AB.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications       |                           |

|-----------------------------|------------------------|--------------------|---------------------------|

| Amplifiers                  | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters             | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DLP® Products               | www.dlp.com            | Broadband          | www.ti.com/broadband      |

| DSP                         | dsp.ti.com             | Digital Control    | www.ti.com/digitalcontrol |

| Clocks and Timers           | www.ti.com/clocks      | Medical            | www.ti.com/medical        |

| Interface                   | interface.ti.com       | Military           | www.ti.com/military       |

| Logic                       | logic.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Power Mgmt                  | power.ti.com           | Security           | www.ti.com/security       |

| Microcontrollers            | microcontroller.ti.com | Telephony          | www.ti.com/telephony      |

| RFID                        | www.ti-rfid.com        | Video & Imaging    | www.ti.com/video          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated