# EDK2329

USER MANUAL

FOR H8S/2329 ON-CHIP FLASH MICROCONTROLLER

# **Preface**

#### **Cautions**

- 1. This document may be, wholly or partially, subject to change without notice.

- 2. All rights reserved. No one is permitted to reproduce or duplicate, in any form, a part or this entire document without Hitachi Micro Systems Europe Limited's written permission.

# **Trademarks**

#### General

All brand or product names used in this manual are trademarks or registered trademarks of their respective companies or organisations.

#### **Specific**

Microsoft, MS and MS-DOS are registered trademarks and Windows and Windows NT are trademarks of Microsoft Corporation.

# **Document Information**

Product Code: D003753\_11

Version: 4.0

Date: 02/05/2003

Copyright © Hitachi Micro Systems Europe Ltd. 1995-2002. All rights reserved.

Global: <a href="http://www.hitachisemiconductor.com">http://www.hitachisemiconductor.com</a>

Europe: <a href="http://www.hmse.com">http://www.hmse.com</a>

# 1. TABLE OF CONTENTS

| 1.   | TABLE OF CONTENTS                               | 3  |

|------|-------------------------------------------------|----|

| 2.   | START-UP INSTRUCTIONS                           | 4  |

| 2.1. | INSTALLING THE EVALUATION DEVELOPMENT KIT (EDK) | 4  |

| 2.2. | SERIAL CONNECTION                               | 4  |

| 2.3. | POWER SUPPLY                                    | 4  |

| 3.   | EDK BOARD LAYOUT                                | 5  |

| 3.1. | EDK BLOCK DIAGRAM                               | 5  |

| 4.   | EDK OPERATION                                   | 6  |

| 4.1. | USER INTERFACE                                  | 6  |

| 4.2. | SERIAL INTERFACE                                | 6  |

| 4.3. | SRAM                                            | 7  |

| 4.4. | MEMORY MAP                                      | 8  |

| 4.5. | SRAM ACCESS TIMING                              | 8  |

| 4.6. | LEDS                                            | 8  |

| 5.   | Board Options                                   | 9  |

| 5.1. | JUMPER LINKS                                    | 9  |

| 5.2. | USER MODE SETTINGS – CJ5                        | 10 |

| 5.3. | EDK OPTIONS - CJ4                               | 10 |

| 5.4. | SERIAL PORT SELECTION                           | 11 |

| 5.5. | FLASH PROGRAMMING HEADER                        | 11 |

| 5.6. | EXTERNAL DEBUG HEADER                           | 12 |

| 5.7. | BOOT CONTROL                                    | 12 |

| 6.   | CODE DEVELOPMENT                                | 14 |

| 6.1. | HMON                                            | 14 |

| 6.2. | MEMORY MAP                                      | 15 |

| 6.3. | ADDITIONAL INFORMATION                          | 16 |

#### 2. START-UP INSTRUCTIONS

# 2.1. Installing the Evaluation Development Kit (EDK)

Please refer to the guick start guide provided for initial installation of the EDK.

A copy of the guick start guide and other information relating to this EDK at:

http://www.hmse.com/products/edk/support.htm

Installing the EDK requires power and serial connection to a host computer.

#### 2.2. SERIAL CONNECTION

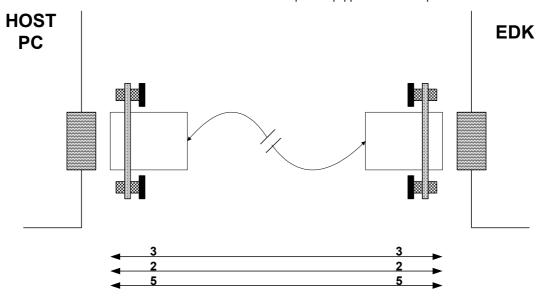

The serial communications cable for connecting the EDK to a host computer is supplied. The serial cable has 1:1 connectivity.

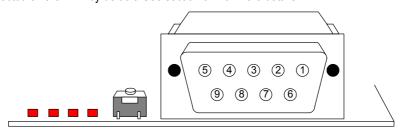

Figure 2-1 shows how to connect the EDK to a PC or notebook computer equipped with a nine pin D connector.

FIGURE 2-1: SERIAL CONNECTION TO PC/NOTEBOOK WITH DB-9 CONNECTOR (SUPPLIED)

#### 2.3. POWER SUPPLY

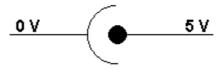

The EDK hardware requires a power supply of +5V. Since total power consumption can vary widely due to external connections, port states, and memory configuration, use a power supply capable of providing at least 500mA at +5V DC  $\pm$  5%.

The design is specified for evaluation of the microcontroller and so does not include circuitry for supply filtering/noise reduction, under voltage protection, over current protection or reversed polarity protection. Caution should be used when selecting and using a power supply.

The power connector on the EDK is a 2.5mm Barrel connector. The center pin is the positive connection.

FIGURE 2-2: POWER SUPPLY CONNECTION

Caution: Existing customers using E6000 products note that the polarity of this board is opposite to that for the E6000. Use of the E6000 power supply with this board will damage both board and power supply.

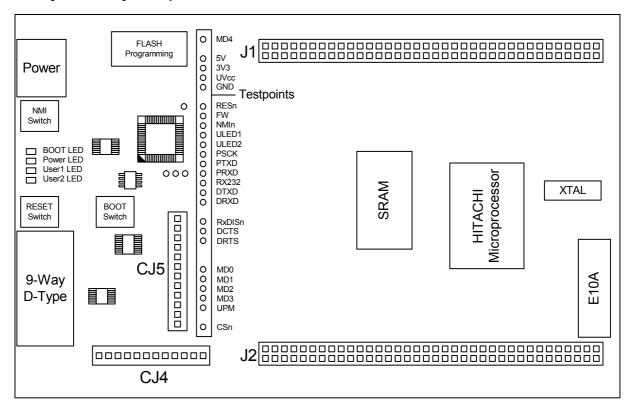

# 3. EDK BOARD LAYOUT

The diagram shows a general layout of the EDK board.

FIGURE 3-1: EDK BOARD LAYOUT

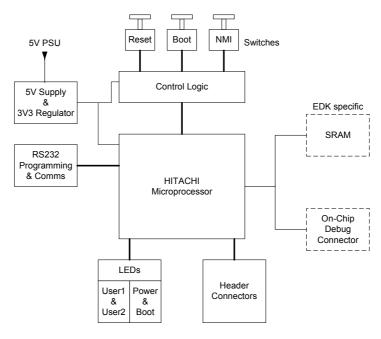

# 3.1. EDK BLOCK DIAGRAM

The diagram shows the connectivity of the components on the EDK board.

FIGURE 3-2: EDK BLOCK DIAGRAM

# 4. EDK OPERATION

# 4.1. USER INTERFACE

The EDK provides three buttons for influencing the operation of the board. The purpose of each button is clearly marked next to it. Refer to the board layout for positions (Figure 3.1)

#### 1. Reset Switch

This button provides the microcontroller with a timed reset pulse of at least 250mS.

#### 2. Boot Switch

This button toggles the operating mode of the microcontroller. A complete description of this function is given in section 5.7.

#### 3. NMI Switch

This button provides a de-bounced signal to the microcontroller for each operation of the button. There is no minimum or maximum activation time for this button.

#### 4.2. SERIAL INTERFACE

The serial interface on the EDK board has several functions. The serial port on the microcontroller directly supports three wire serial interfaces. Options are provided on the board for the user to write handshaking routines using standard port pins. Other board option links allow users to control the entry and exit from boot mode using the same handshaking signals. Refer to section 5.4 for details on setting serial interface options.

#### 4.2.1. CONNECTOR PIN DEFINITIONS

The EDK RS232 interface conforms to Data Communication Equipment (DCE) format allowing the use of 1-1 cables when connected to Data Terminal Equipment (DTE) such as an IBM PC. The cable used to connect to the EDK will affect the available board options. A fully wired cable can allow handshaking between the microcontroller and the host PC, subject to setting the board options and the availability of suitable host software. Handshaking is not supported as standard on the microcontroller so for normal use a minimal three-wire cable can be used. The minimum connections are unshaded in the following table.

| EDK DB9<br>Connector Pin | Signal             | Host DB9<br>Connector Pin |

|--------------------------|--------------------|---------------------------|

| 1                        | No Connection      | 1                         |

| 2                        | EDK Tx Host Rx     | 2                         |

| 3                        | EDK Rx Host Tx     | 3                         |

| 4                        | No Connection      | 4                         |

| 5                        | Ground             | 5                         |

| 6                        | No Connection      | 6                         |

| 7                        | * EDK CTS Host RTS | 7                         |

| 8                        | * EDK RTS Host CTS | 8                         |

| 9                        | No Connection      | 9                         |

**TABLE 4-1: RS232 INTERFACE CONNECTIONS**

<sup>\*</sup> These are not connected on the EDK by default. See section 5.4 for more details.

FIGURE 4-1: EDK SERIAL PORT PIN NUMBERING

#### 4.2.2. CRYSTAI CHOICE

The operating crystal frequency has been chosen to support the fastest operation with the fastest serial operating speeds. The value of the crystal is 22.1184MHz.

The following table shows the baud rates and Baud Rate Register (BRR) setting required for each communication rate using the above default operating speed. It also confirms the resultant baud rate and the bit error rate that can be expected.

|                 | Baud Rate Register Settings for Serial Communication Rates |                |            |             |                |            |             |                |            |             |                |            |

|-----------------|------------------------------------------------------------|----------------|------------|-------------|----------------|------------|-------------|----------------|------------|-------------|----------------|------------|

| SMR<br>Setting: |                                                            | 0              |            |             | 1              |            |             | 2              |            |             | 3              |            |

| Comm.<br>Baud   | BRR setting                                                | Actual<br>Rate | ERR<br>(%) | BRR setting | Actual<br>Rate | ERR<br>(%) | BRR setting | Actual<br>Rate | ERR<br>(%) | BRR setting | Actual<br>Rate | ERR<br>(%) |

| 110             | invalid                                                    | invalid        | invalid    | invalid     | invalid        | invalid    | invalid     | invalid        | invalid    | 97          | 110            | 0.19       |

| 300             | invalid                                                    | invalid        | invalid    | invalid     | invalid        | invalid    | 143         | 300            | 0.00       | 35          | 300            | 0.00       |

| 1200            | invalid                                                    | invalid        | invalid    | 143         | 1200           | 0.00       | 35          | 1200           | 0.00       | 8           | 1200           | 0.00       |

| 2400            | invalid                                                    | invalid        | invalid    | 71          | 2400           | 0.00       | 17          | 2400           | 0.00       | 4           | 2160           | -10.00     |

| 4800            | 143                                                        | 4800           | 0.00       | 35          | 4800           | 0.00       | 8           | 4800           | 0.00       | 1           | 5400           | 12.50      |

| 9600            | 71                                                         | 9600           | 0.00       | 17          | 9600           | 0.00       | 4           | 8640           | -10.00     | 0           | 10800          | 12.50      |

| 19200           | 35                                                         | 19200          | 0.00       | 8           | 19200          | 0.00       | 1           | 21600          | 12.50      | 0           | 10800          | -43.75     |

| 38400           | 17                                                         | 38400          | 0.00       | 4           | 34560          | -10.00     | 0           | 43200          | 12.50      | invalid     | invalid        | invalid    |

| 57600           | 11                                                         | 57600          | 0.00       | 2           | 57600          | 0.00       | 0           | 43200          | -25.00     | invalid     | invalid        | invalid    |

| 115200          | 5                                                          | 115200         | 0.00       | 1           | 86400          | -25.00     | invalid     | invalid        | invalid    | invalid     | invalid        | invalid    |

| 230400*         | 2                                                          | 230400         | 0.00       | 0           | 172800         | -25.00     | invalid     | invalid        | invalid    | invalid     | invalid        | invalid    |

| 460800*         | 1                                                          | 345600         | -25.00     | invalid     | invalid        | invalid    | invalid     | invalid        | invalid    | invalid     | invalid        | invalid    |

TABLE 4-2 CRYSTAL FREQUENCIES FOR RS232 COMMUNICATION

The default communication rate for the EDK is indicated by the shaded selection.

The user may replace the HC49/U surface mounted AT cut crystal with another of similar type within the operating frequency of the microcontroller device. Please refer to the hardware manual for the microcontroller for the valid operating range.

Alternatively the user may fit an oscillator module – or provide an external clock source. When providing an oscillator module or external source it is highly recommended that the load capacitors for the AT crystal are removed from the PCB. These are physically placed within the PCB outline of the oscillator module for easy location and to ensure they are removed when using this option.

When changing the crystal frequency the pre-loaded debugging monitor will not function. In this situation the user is responsible for providing code to evaluate the device away from the default operating speed.

#### 4.2.3. REMOVABLE COMPONENT INFORMATION.

This information is provided to allow the replacement of components removed from the board as described in section 4.2.2.

| Component            | Cct. Ref | Value | Rating       | Manufacturer         |

|----------------------|----------|-------|--------------|----------------------|

| Load Resistor (X1)   | R20      | 1ΜΩ   | 0805 1%      | Welwyn WCR Series    |

| Load capacitors (X1) | C13.C14  | 12pF  | 0603 10% 25V | AVX 0603 3 A 150 KAT |

TABLE 4-3: REMOVABLE COMPONENT INFORMATION

Care must be taken not to damage the tracking around these components. Only use soldering equipment designed for surface mount assembly and rework.

#### 4.3. SRAM

The SRAM device fitted to the board is a 4Mbit device allowing 256k x 16 operation.

The SRAM is mapped to area 0 via chip select 0 (port PG4), with a usable address range of H'00080000 – H'000BFFFF using address signals A1 – A18.

Glue logic provides the required SRAM control signals from the H8S/2329 micon.

<sup>\*</sup> Note: The device used to convert the RS232 serial information to logic signals for the microcontroller is limited to 120kBaud. The rates above this level can only be utilised if the user provides direct logic level communications.

#### 4.4. MEMORY MAP

Table 4-4 illustrates the EDK memory map for mode 6.

| Section End   | Section Allocation                   |

|---------------|--------------------------------------|

| Section Start | Section Anocation                    |

| H'0000000     | On-chip ROM                          |

| H'0000FFFF    | On-chip KOW                          |

| H'00010000    | On-chip ROM / External Address Space |

| H'0005FFFF    | On-emp ROW / External Address Space  |

| H'00060000    | Reserved area                        |

| H'0007FFFF    | Reserved area                        |

| H'00080000    | External Address Space               |

| H'00FF73FF    | External Address Space               |

| H'00FF7400    | Reserved Area                        |

| H'00FF7BFF    | Reserved Area                        |

| H'00FF7C00    | On-chip RAM                          |

| H'00FFFBFF    | On-chip KAW                          |

| H'00FFFC00    | Extannal Address Chase               |

| H'00FFFE4F    | External Address Space               |

| H'00FFFE50    | Internal IO Degisters                |

| H'00FFFF07    | Internal IO Registers                |

| H'00FFFF08    | External Address Space               |

| H'00FFFF27    | External Address Space               |

| H'00FFFF28    | Internal IO Registers                |

| H'00FFFFFF    | internal to Registers                |

TABLE 4-4: MEMORY MAP (DEFAULT MODE 6)

# 4.5. SRAM Access Timing

External access timing is defined by several registers, allowing different types of devices to be addressed. The registers for the selection of wait states and signal extensions are given below with recommended values for the EDK.

| Register | Address | Recommended<br>Setting for EDK | Function                                                                     |

|----------|---------|--------------------------------|------------------------------------------------------------------------------|

| ABWCR    | H'FED0  | H'F0                           | Bus Width Control Register. Enables 16 bit access for CS0 space.             |

| ASTCR    | H'FED1  | H'FF                           | Access State Control Register. Initialised to 3-state access.                |

| BCRH     | H'FED4  | H'D0                           | 16b R/W access. Specifies idle cycles.                                       |

| PADDR    | H'FEB9  | H'07                           | Port A Data Direction Register. Enables address signals A(18:16) for output. |

| PBDDR    | H'FEBA  | H'FF                           | Port B Data Direction Register. Enables address signals A(15:8) for output.  |

| PCDDR    | H'FEBB  | H'FF                           | Port C Data Direction Register. Enables address signals A(7:0) for output.   |

| PGDDR    | H'FEBF  | H'01                           | Port G Data Direction Register. CSn(0) output pin.                           |

| WCRL     | H'FED3  | H'FD                           | 16b R/W access. Specifies 1 wait cycle for CS0 space.                        |

TABLE 4-5: SRAM ACCESS CONTROL REGISTERS

Please refer to the hardware manual for the microcontroller for more information on these register settings.

#### 4.6. LEDs

The EDK has four red LEDs. The function of each LED is clearly marked on the silk screen of the PCB. Please refer to the board layout diagram for position information (Figure 3.1).

When the board is connected to a power source the Power (PWR) led will illuminate. The Boot mode indication LED will illuminate when the microcontroller has been placed into Boot mode. Please see section 5.7 for more details of this function.

There are two LEDs dedicated for user control these are marked USR1 and USR2. Each LED will illuminate when the port pin is in a logical high state.

The user LEDs are connected to the following ports:

| LED<br>Identifier | Port<br>Pin | Microcontroller<br>Pin | Pin Functions on Port Pin  |

|-------------------|-------------|------------------------|----------------------------|

| USR1              | P21         | 78                     | P21 / PO1 / TIOCB3         |

| USR2              | P22         | 77                     | P22 / PO2 / TIOCC3 / TMRI0 |

TABLE 4-6: LED PORT CONNECTIONS

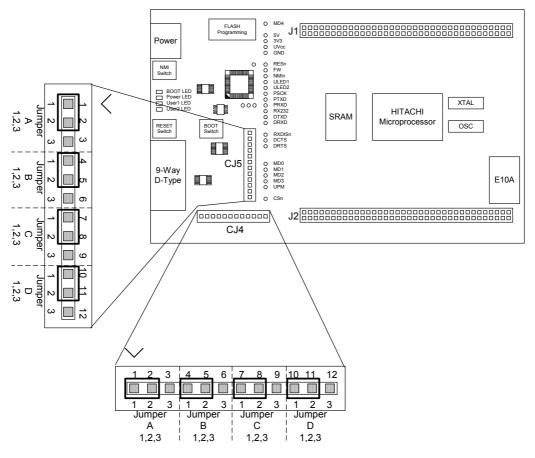

# 5. BOARD OPTIONS

The EDK has a number of configuration settings set by jumpers CJ4 (A, B, C, D), CJ5 (A, B, C, D) and zero-ohm links. Common EDK functions can be set using the jumpers as described in sections 5.3 and 5.2. The additional zero-ohm links provide additional features that may be required to interface with other systems.

All the Jumper link settings are three pin options. There are four sets of options on each header.

The headers are numbered from 1 to 12 with pin 1 marked on the PCB by an arrow pointing to the pin. The diagram below shows the numbering of these jumper links and indicates jumpers fitted 1-2 for each three-pin jumper.

#### 5.1. JUMPER LINKS

FIGURE 5-1: JUMPER CONFIGURATION

The following tables define each jumper and its settings.

# 5.2. USER MODE SETTINGS - CJ5

CJ5 is used to set the operating mode of the microcontroller.

These jumpers must be fitted at all times to ensure correct operation of the EDK.

| Jumper                | Function                | Setting 1-2     | Setting 2-3    |

|-----------------------|-------------------------|-----------------|----------------|

| CJ 5-A<br>Default 2-3 | User Mode Setting Bit 0 | MD0 pulled High | MD0 pulled Low |

| CJ 5-B<br>Default 1-2 | User Mode Setting Bit 1 | MD1 pulled High | MD1 pulled Low |

| CJ 5-C<br>Default 1-2 | User Mode Setting Bit 2 | MD2 pulled High | MD2 pulled Low |

| CJ 5-D<br>Default 1-2 | User Mode Setting Bit 3 | MD3 pulled High | MD3 pulled Low |

TABLE 5-1: USER MODE: JUMPER SETTINGS (DEFAULT SETTINGS IN BOLD)

The default settings indicated in bold text place the microcontroller into Mode 6, i.e. advanced expanded mode with on-chip ROM enabled.

Note: CJ5-D is not connected to any signal on the EDK as the H8S/2329 does not utilise a MD3 pin.

# 5.3. EDK OPTIONS – CJ4

The EDK options provide access to commonly used features of the EDK range.

These jumpers must be fitted at all times to ensure correct operation of the EDK.

| Jumper                | Function                       | Setting 1-2                                                                         | Setting 2-3                                                                                        |

|-----------------------|--------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| CJ 4-A<br>Default 2-3 | Serial Receive<br>Source       | Disables the RS232 receive signal to enable the use of the Flash Programming Header | Enables the RS232 receive signal.  The Flash Programming Header *1 must not be used in this state. |

| CJ 4-B<br>Default 2-3 | User<br>Programming<br>Mode *2 | Enables E10A interface.                                                             | Disables E10A Interface.                                                                           |

| CJ 4-C<br>Default 2-3 | CSn                            | SRAM enabled when H8S/2329<br>CSn(0) signal is asserted                             | SRAM Disabled                                                                                      |

| CJ 4-D<br>Default 1-2 | No Connection                  | No Connection                                                                       | No Connection                                                                                      |

TABLE 5-2: BOARD OPTION: JUMPER SETTINGS (DEFAULT SETTINGS IN BOLD)

The following table lists the connections to each jumper pin.

| Pin | Net Name      | Description                                                 |

|-----|---------------|-------------------------------------------------------------|

| 1   | UVCC          | Microcontroller Supply Voltage                              |

| 2   | RXDISn        | Disable Flash Header functions. Pulled low. (Enables RX232) |

| 3   | No Connection | No Connection                                               |

| 4   | UVCC          | Microcontroller Supply Voltage                              |

| 5   | UPM           | CPLD Controlled option to set Flash Write (FW). Pulled low. |

|     |               | E10A Enable / Disable Signal.                               |

| 6   | No Connection | No Connection                                               |

| 7   | PG4           | Microcontroller CSn(0) signal                               |

| 8   | CSn           | SRAM CSn signal                                             |

| 9   | No Connection | No Connection                                               |

| 10  | No Connection | No Connection                                               |

| 11  | No Connection | No Connection                                               |

| 12  | No Connection | No Connection                                               |

<sup>\*1</sup> See section 5.5

<sup>\*2</sup> Please note function of CJ4-B is different to the majority of EDKs where an FWE pin enables and disables the flash write protect function.

#### 5.4. SERIAL PORT SELECTION

The programming serial port is connected to the RS232 connector by default. This allows direct programming of the EDK using the supplied software tools. A secondary serial port is available on the microcontroller and can be connected to the RS232 connector by changing some board option links. The additional port option allows the user to write messages or connect to other devices via the serial port while programming support is provided by the Flash programming header.

The following surface mount, zero-ohm link settings are fitted by default and connect the RS232 header to the programming serial port of the microcontroller.

| Zero-ohm<br>Link ID | Default    | Function                         | Microcontroller<br>Port Pin |

|---------------------|------------|----------------------------------|-----------------------------|

| CR20                | Fitted     | Transmit data from EDK           | P31                         |

| CR23                | Fitted     | Receive data to EDK              | P33                         |

| CR19                | Not Fitted | Alternate Transmit data from EDK | P30                         |

| CR22                | Not Fitted | Alternate Receive data to EDK    | P32                         |

TABLE 5-3: OPTION LINKS - DEFAULT SETTINGS

To enable the use of this alternate port the user must change the settings to those in the following table.

| Zero-ohm<br>Link ID | Default    | Function                         | Microcontroller<br>Port Pin |

|---------------------|------------|----------------------------------|-----------------------------|

| CR20                | Not Fitted | Transmit data from EDK           | P31                         |

| CR23                | Not Fitted | Receive data to EDK              | P33                         |

| CR19                | Fitted     | Alternate Transmit data from EDK | P30                         |

| CR22                | Fitted     | Alternate Receive data to EDK    | P32                         |

TABLE 5-4: OPTION LINKS - ALTERNATE SERIAL PORT

The user may implement a handshaking protocol on the EDK. This is not supported with the software tools supplied. To support this option two spare port pins have been allocated on the microcontroller. Using these port pins the CTS and RTS lines of the host serial interface can be controlled.

The user may also control the operation of the board via the same handshaking lines. This is not supported with the software tools supplied but may be written by the user. Using the CTS line the user may simulate pressing the boot button, see section:5.7. This will cause the EDK to swap into and out of Boot mode on each low-level activation of CTS. Feedback of the current mode is provided on the RTS line. A high level indicates boot mode and a low level indicates user mode.

The following settings are made by default, and ensure that there are no conflicts on unnecessary microcontroller pins.

| Zero-ohm<br>Link ID | Default    | Function                                    | Microcontroller<br>Port Pin |

|---------------------|------------|---------------------------------------------|-----------------------------|

| CR12                | Not Fitted | Mode State out from EDK                     | N/A (From CPLD*)            |

| CR7                 | Not Fitted | Change Mode request to EDK                  | N/A (From CPLD*)            |

| CR16                | Not Fitted | Alternate RTS232 – Ready to send – from EDK | P65                         |

| CR13                | Not Fitted | Alternate CTS232 – Clear to send – to EDK   | P64                         |

TABLE 5-5: OPTION LINKS - SERIAL PORT CONTROL

Note: These setting pairs are exclusive:

If CR12 and CR7 are fitted; CR16 and CR13 must not be fitted. If CR16 and CR13 are fitted; CR12 and CR7 must not be fitted.

#### 5.5. FLASH PROGRAMMING HEADER

The Flash Programming header is used with the Hitachi Flash Debug Board (FDB). The FDB is a USB based programming tool for control and programming of Hitachi microcontrollers, available separately from Hitachi. This header provides direct access for the FDB to control the EDK microcontroller.

To utilise this header the user must make the following changes to the board configuration.

- Disable the RX232 signal from the RS232 transceiver.

Jumper link CJ4-A is provided for this purpose. Please refer to section 5.3.

- 2. Disable User Program Mode using jumper CJ4-B. Please refer to section 5.3.

Caution: Do not operate the board with the user mode jumpers removed and the FDB disconnected as the microcontroller mode pins will float to an indeterminate state. This may damage the microcontroller device.

<sup>\*</sup> See section 5.7

#### 5.6. EXTERNAL DEBUG HEADER

The External debug header may be used with the Hitachi E10A Debugger or a third party debugger.

The E10A is an on-chip debug emulator available separately from Hitachi.

This header provides direct access for the debugger to control the EDK microcontroller.

To utilise this header the user must enable the E10A interface via jumper CJ4-B. Please refer to section 5.3.

#### 5.7. BOOT CONTROL

The method for placing the microcontroller device in to Boot mode for reprogramming has been incorporated into a complex programmable logic device (CPLD). This is not necessary for most user designs but allows a measure of increased flexibility for the EDK designs. Mode transitions including boot mode transitions only require the reset to be held active while the mode settings are presented. On releasing reset the microcontroller will be in the required mode.

The logic design detects a power up event and provides a timed reset pulse to guarantee the reset of the device. At the end of the rest pulse the processor will be placed in user mode and any code in the device will execute.

During user mode the NMI button can be pressed at any time. This will provide a single de-bounced NMI interrupt to the device.

Pressing the boot button will cause the boot mode controller to reset the device and, during the reset period, present the required mode settings to start the device in boot mode. At the end of the reset period the boot mode settings will have been latched into the device which will then be ready to accept a boot mode connection via the RS232 interface or the flash programming header. Pressing the boot button during a normal reset will not cause the EDK to enter boot mode.

The boot mode settings are fixed at mode 2. The required mode settings are made using a tri-state capable buffer.

Note: The boot control device is programmed to support all possible EDK products.

For this reason the reset pulse is over 500ms. Repetitive activation of either the Boot or Reset buttons will restart the reset timer and extend the reset period. Pressing the boot button within the 500mS period of a reset will not cause the board to enter boot mode.

#### **5.7.1. CPLD CODE**

The code is based upon a four state machine providing a guaranteed reset period that can be extended by holding the relevant control input in the active state. When released the timer will extend the reset for approximately 500mS.

The states are split into two functions, one for User mode and one for Boot mode. The first state of each is used to hold the reset line active. When the timer expires then the second state is used to hold the device in the selected mode and wait for an external control signal to either move back into the user reset state or into the boot reset state.

# 5.7.2. STATE DIAGRAM

# Boot Mode Controller : Positive Logic Walting (CTS+BootSw) ./Res Res ResSw ./Res Res Reset Timer Res Reset Timer (All solid transition lines) Reset Reset

FIGURE 5-2: CPLD STATE DIAGRAM

# 6. CODE DEVELOPMENT

# 6.1. **HMON**

#### 6.1.1. MODE SUPPORT

The HMON library is built to support modes 4, 5, 6 and 7.

#### 6.1.2. Breakpoint Support

H8S/2329 has no break controller, therefore there no breakpoints can be set in flash. Code located in RAM may have multiple breakpoints, and is limited only by the size of the On-Chip RAM.

#### 6.1.3. CODE LOCATED IN FLASH / ROM

This device does not have a PC break controller. Breakpoints are limited to compiled in Trap instructions. HEW will not allow breakpoints to be set in the ROM/FLASH area.

#### 6.1.4. CODE LOCATED IN RAM

Double clicking in the breakpoint column in the code sets the breakpoint. Breakpoints will remain unless they are double clicked to remove them.

# 6.1.5. HMON CODE SIZE

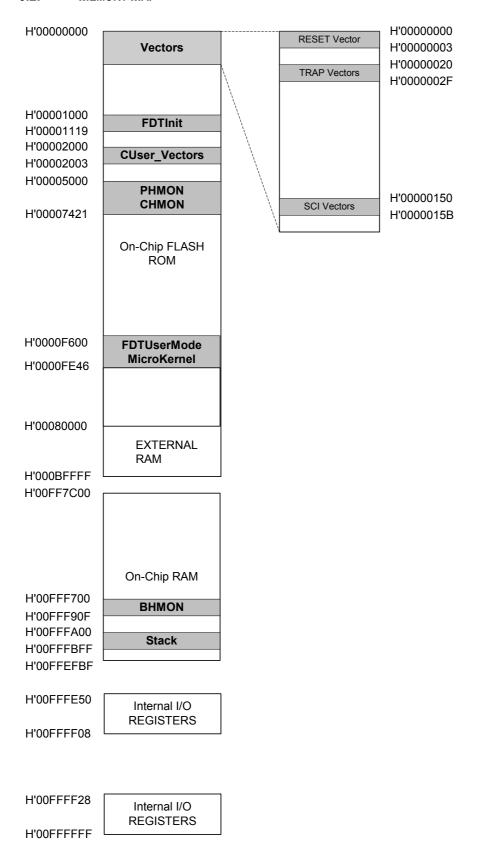

HMON is built along with the debug code. Certain elements of the HMON code must remain at a fixed location in memory. The following table details the HMON components and their size and location in memory. For more information, refer to the map file when building code.

| Section                | Description                                                                                                                                                      | Start Location | Size<br>(H'bytes) |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|

| RESET_VECTOR           | HMON Reset Vector (Vector 0) Required for Startup of HMON                                                                                                        | H, 000000000   | 4                 |

| TRAP_VECTORS           | Trap Vectors (Vector 8, 9, 10, 11) Required by HMON to create Trap Breakpoints in RAM                                                                            | H' 00000020    | 10                |

| SCI_VECTORS            | HMON Serial Port Vectors (Vector 84, 85, 86, 87) Used by HMON when EDK is configured to connect to the default serial port.                                      | H' 00000150    | С                 |

| PHMON                  | HMON Code                                                                                                                                                        | H' 00005000    | 72D9              |

| CHMON                  | HMON Constant Data                                                                                                                                               | H' 000072DA    | 147               |

| BHMON                  | HMON Uninitialised data                                                                                                                                          | H' 00FFF000    | 20F               |

| FDTInit                | FDT User Mode Kernel. This is at a fixed location and must not be moved. Should the kernel need to be moved it must be re-compiled.                              | H' 00001000    | 11E               |

| FDTUserModeMicroKernel | FDT User Mode Kernel. This is at a fixed location and must not be moved. Should the kernel need to be moved it must be re-compiled.                              | H' 0000F600    | 847               |

| CUser_Vectors          | Pointer used by HMON to point to the start of user code. This is at a fixed location and must not be moved for the Reset CPU, and Go Reset commands to function. | H' 00002000    | 4                 |

# 6.2. MEMORY MAP

#### 6.2.1. BAUD RATE SETTING

HMON has initially set to connect at 115200Baud. Should the user wish to change this, the value for the BRR in HMONserialconfiguser.c will need to be changed and the project re-built. Please refer to the HMON User Manual for further information.

#### 6.2.2. INTERRUPT MASK SECTIONS

HMON has an interrupt priority of 6. The serial port has an interrupt priority of 7. Modules using interrupts should be set to lower than this value (6 or below), so that serial communications and debugging capability is maintained.

#### 6.3. ADDITIONAL INFORMATION

For details on how to use Hitachi Embedded Workshop 2(HEW2), with HDI-m, the EDK's resident debugger, refer to the HEW2 manual available on the CD or from the web site.

For information about the H8S/2329 series microcontrollers refer to the H8S/2329 Series Hardware Manual

For information about the H8S/2000 assembly language, refer to the H8S/2000 Series Programming Manual

Further information available for this product can be found on the HMSE web site at:

http://www.hmse.com/products/edk/support.htm

General information on Hitachi Microcontrollers can be found at the following URLs.

Global: http://www.hitachisemiconductor.com

Europe: <a href="http://www.hmse.com">http://www.hmse.com</a>