# SEMICONDUCTOR

# **Radio Interface and Twin Synthesiser**

Supersedes February 1997 edition, DS4288 - 1.4

DS4288 - 2.0 January 1998

ACE9030

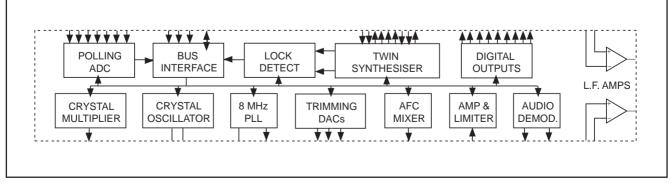

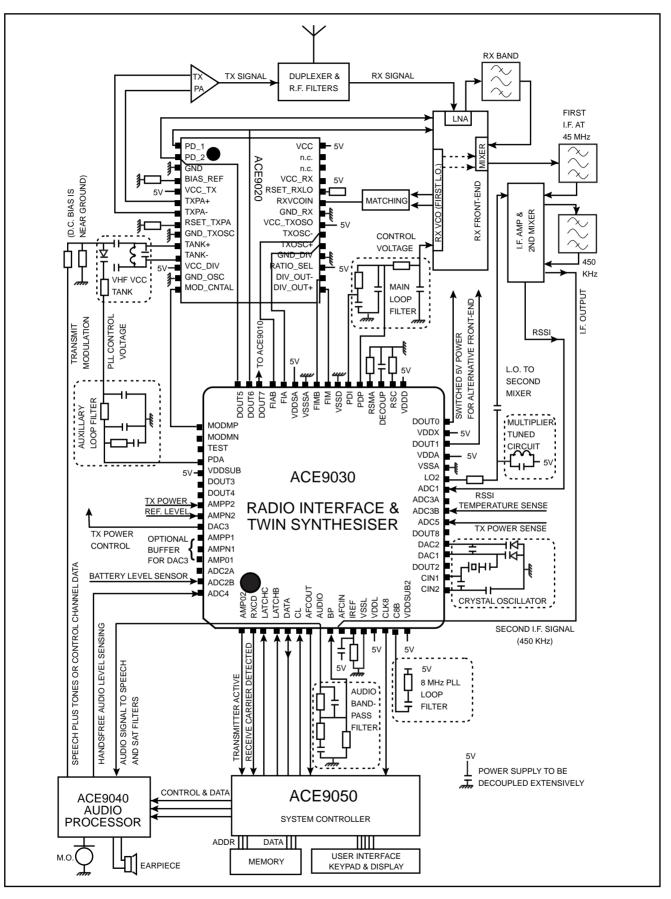

ACE9030 is a combined radio interface circuit and twin synthesiser, intended for use in a cellular telephone.

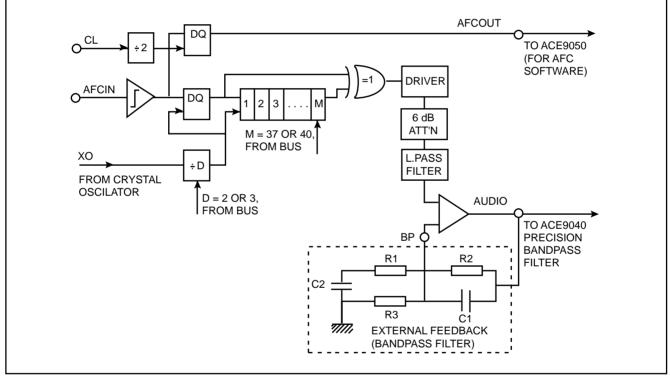

The radio interface section contains circuits to monitor and control levels such as transmit power in the telephone, circuits to demodulate the frequency modulated signal to audio, and a crystal oscillator with a frequency multiplier.

The Main synthesiser has normal and fractional-N modes both with optional speed-up to select the desired channel. The Auxiliary synthesiser is used for the transmit-receive offset and for modulation.

Both sections are controlled by a serial bus and have software selected power saving modes for battery economy. The circuit techniques used have been chosen to minimise external components and at the same time give very high performance.

# **FEATURES**

- Low Power Low Voltage (3.6 to 5.0 V) Operation

- Serial Bus Controlled Power Down Modes

- Simple Programming Format

- Reference Crystal Oscillator

- Frequency Multiplier for LO2 Signal

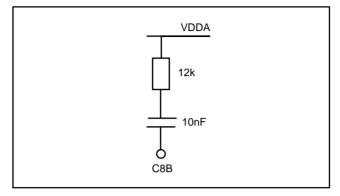

- 8.064 MHz Output for External Microcontroller

- Main Synthesiser with Fractional-N Option

- Auxiliary Synthesiser

- Main Synthesiser Speed-up Options

- FM Discriminator for 450 kHz or 455 kHz I.F. Signal

- Radio System Control Interface

- Part of the ACE Integrated Cellular Phone Chipset

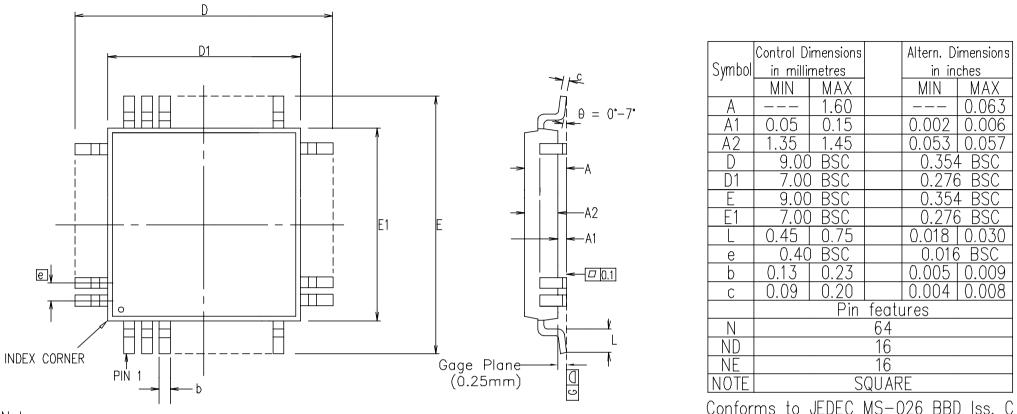

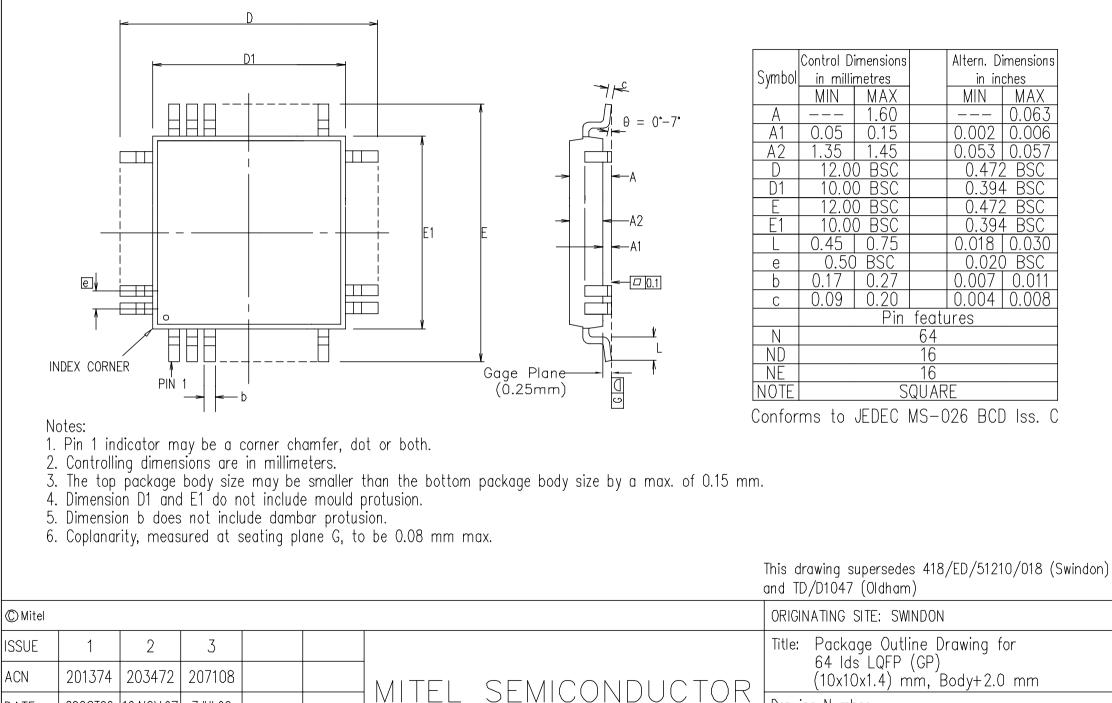

- TQFP 64 pin 0.4 mm and 0.5 mm pitch packages

# **RELATED PRODUCTS**

ACE9030 is part of the following chipset:

- ACE9020 Receiver and Transmitter Interface

- ACE9040 Audio Processor

- ACE9050 System Controller and Data Modem

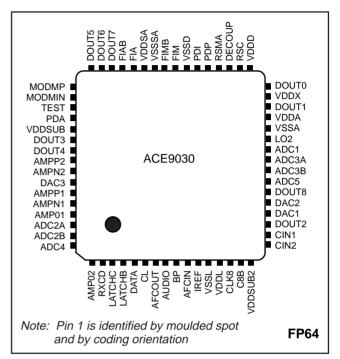

Fig.1 Pin connections - top view

#### **APPLICATIONS**

- AMPS and TACS Cellular Telephone

- Two-way Radio Systems

# **ORDERING INFORMATION**

Industrial temperature range TQFP 64 lead 10 x 10 mm, 0.5 mm pitch ACE9030M/IW/FP1N - shipped in trays and dry packed ACE9030M/IW/FP1Q - tape & reel and dry packed TQFP 64 lead 7 x 7 mm, 0.4 mm pitch ACE9030M/IW/FP2N - shipped in trays and dry packed ACE9030M/IW/FP2Q - tape & reel and dry packed

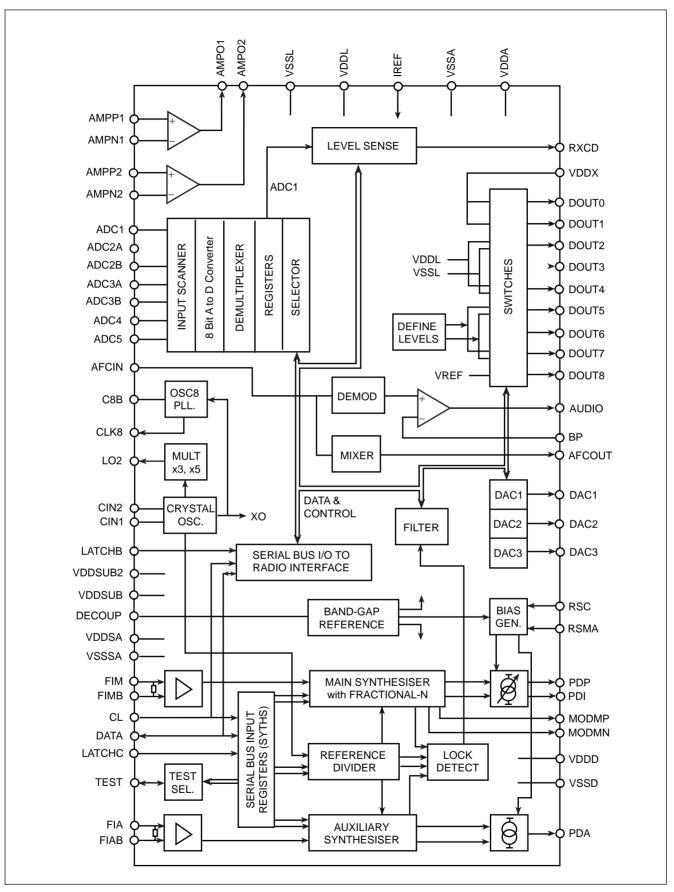

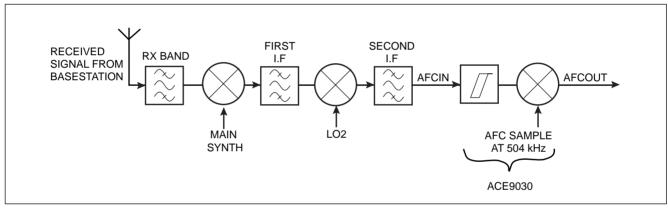

Fig.3 ACE9030 Block diagram

# **PIN DESCRIPTIONS**

The relevant supplies ( $V_{DD}$ ) and grounds ( $V_{SS}$ ) for each circuit function are listed. All  $V_{DD}$  and  $V_{SS}$  pins should be used.

| Pin No.  | Name    | Description                                                                                                       | VDD   | VSS   |

|----------|---------|-------------------------------------------------------------------------------------------------------------------|-------|-------|

| 1        | AMPO2   | LF amplifier 2 output.                                                                                            | VDDA  | VSSA  |

| 2        | RXCD    | Receive carrier detect (ADC1 comparator) output.                                                                  | VDDL  | VSSL  |

| 3        | LATCHC  | Synthesiser programme enable input.                                                                               | VDDL  | VSSL  |

| 4        | LATCHB  | Radio interface programme enable input.                                                                           | VDDL  | VSSL  |

| 5        | DATA    | Serial data; programming input, results output.                                                                   | VDDL  | VSSL  |

| 6        | CL      | Clock input for programming bus and for I.F. sampling.                                                            | VDDL  | VSSL  |

| 7        | AFCOUT  | Output from AFC amplifier after sampling.                                                                         | VDDL  | VSSL  |

| 8        | AUDIO   | Output from f.m. discriminator after filtering.                                                                   | VDDA  | VSSA  |

| 9        | BP      | Feedback input to audio bandpass filter.                                                                          | VDDA  | VSSA  |

| 10       | AFCIN   | Input to AFC amplifier and f.m. discriminator.                                                                    | VDDL  | VSSL  |

| 11       | IREF    | Bias current input for radio interface, connect setting resistor to ground.                                       | _     | VSSA  |

| 12       | VSSL    | Ground for radio interface logic.                                                                                 | _     | _     |

| 13       | VDDL    | Power supply to radio interface logic.                                                                            | _     | _     |

| 14       | CLK8    | Output clock at 8.064 MHz, locked to crystal.                                                                     | VDDL  | VSSL  |

| 15       | C8B     | 8.064 MHz oscillator charge pump output and control voltage input.                                                | VDDA  | VSSA  |

| 16       | VDDSUB2 | Second connection for clean positive supply to bias substrate.                                                    | VDDA  | VSSA  |

| 17       | CIN2    | Connection for crystal oscillator.                                                                                | VDDL  | VSSL  |

| 18       | CIN1    | Connection for crystal oscillator.                                                                                | VDDL  | VSSL  |

| 19       | DOUT2   | Digital control output 2.                                                                                         | VDDL  | VSSL  |

| 20       | DAC1    | Analog control output 1.                                                                                          | VDDA  | VSSA  |

| 21       | DAC2    | Analog control output 2.                                                                                          | VDDA  | VSSA  |

| 22       | DOUT8   | Digital control output 8.                                                                                         | VDDA  | VSSA  |

| 23       | ADC5    | Analog to digital converter input 5.                                                                              | VDDA  | VSSA  |

| 24       | ADC3B   | Analog to digital converter input 3.                                                                              | VDDA  | VSSA  |

| 25       | ADC3A   | Analog to digital converter input 3A.                                                                             | VDDA  | VSSA  |

| 26       | ADC1    | Analog to digital converter input 3A.                                                                             | VDDA  | VSSA  |

| 20       | LO2     | Output from crystal frequency multiplier.                                                                         | VDDA  | VSSA  |

| 28       | VSSA    | Ground for radio interface analog parts.                                                                          |       | V00A  |

| 20       | VDDA    | Power supply to radio interface analog parts.                                                                     |       | _     |

| 30       | DOUT1   | Digital control output 1.                                                                                         | VDDX  | _     |

| 31       | VDDX    | Power supply to DOUT1 and DOUT2 switches.                                                                         | VDDA  | _     |

| 32       | DOUT0   | Digital control output 0.                                                                                         | VDDX  | _     |

| 33       | VDDD    |                                                                                                                   | VDDA  | _     |

| 33       | RSC     | Power supply to synthesisers, except input buffers and the bandgap.                                               | _     | VSSSA |

| 34       | DECOUP  | Fractional-N compensation bias current, resistor to ground.<br>Bandgap reference decoupling capacitor connection. | VDDSA | VSSSA |

| 36       | RSMA    | Bias current for synthesiser charge pumps, resistor to ground.                                                    | VDDSA | VSSSA |

| 30       | PDP     | Main synthesiser proportional charge pump output.                                                                 | VDDD  | VSSD  |

| 38       | PDF     | Main synthesiser proportional charge pump output.                                                                 | VDDD  | VSSD  |

| 39       | VSSD    |                                                                                                                   | VDDD  | V33D  |

|          |         | Ground for synthesisers, except input buffers and the bandgap.                                                    |       | VSSSA |

| 40       | FIM     | Main synthesiser positive input from prescaler.                                                                   | VDDSA |       |

| 41       | FIMB    | Main synthesiser negative input from prescaler.                                                                   | VDDSA | VSSSA |

| 42       | VSSSA   | Ground for FIM and FIA input buffers and the bandgap.                                                             | _     | _     |

| 43       | VDDSA   | Power for FIM and FIA input buffers and the bandgap.                                                              |       |       |

| 44       | FIA     | Auxiliary synthesiser positive input from VCO.                                                                    |       | VSSSA |

| 45       | FIAB    | Auxiliary synthesiser negative input from VCO.                                                                    | VDDSA | VSSSA |

| 46       | DOUT7   | Digital control output 7.                                                                                         | VDDD  | VSSD  |

| 47       | DOUT6   | Digital control output 6.                                                                                         | VDDD  | VSSD  |

| 48       |         | Digital control output 5.                                                                                         | VDDD  | VSSD  |

| 49<br>50 | MODMP   | Modulus control output to prescaler - positive sense.                                                             | VDDD  | VSSD  |

| 50<br>51 | MODMN   | Modulus control output to prescaler - negative sense.                                                             | VDDD  | VSSD  |

| 51       | TEST    | Test input and output for synthesisers.                                                                           | VDDD  | VSSD  |

| 52       | PDA     | Auxiliary synthesiser charge pump output.                                                                         | VDDD  | VSSD  |

| 53       | VDDSUB  | Clean positive supply to bias substrate.                                                                          |       |       |

| 54       | DOUT3   | Digital control output 3.                                                                                         | VDDL  | VSSL  |

| 55       | DOUT4   | Digital control output 4.                                                                                         | VDDL  | VSSL  |

| 56       | AMPP2   | LF amplifier 2 positive input.                                                                                    | VDDA  | VSSA  |

| 57       | AMPN2   | LF amplifier 2 negative input.                                                                                    | VDDA  | VSSA  |

| 58       | DAC3    | Analog control output 3.                                                                                          | VDDL  | VSSL  |

| 59       | AMPP1   | LF amplifier 1 positive input.                                                                                    | VDDA  | VSSA  |

| 60       | AMPN1   | LF amplifier 1 negative input.                                                                                    | VDDA  | VSSA  |

| 61       | AMPO1   | LF amplifier 1 output.                                                                                            | VDDA  | VSSA  |

| 62       | ADC2A   | Analog to digital converter input 2A.                                                                             | VDDA  | VSSA  |

| 63       | ADC2B   | Analog to digital converter input 2B.                                                                             | VDDA  | VSSA  |

| 64       | ADC4    | Analog to digital converter input 4.                                                                              | VDDA  | VSSA  |

# **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage from ground (any $V_{DD}$ to any $V_{SS}$ ) | -0.3 V to $+6.0$ V                   |

|------------------------------------------------------------|--------------------------------------|

| Supply voltage difference                                  | – 0.3 V to + 0.3 V                   |

| (any $V_{DD}$ to any other $V_{DD}$ )                      |                                      |

| Input voltage                                              | $V_{SS} - 0.3$ V to $V_{DD} + 0.3$ V |

| (any input pin to its local V <sub>ss</sub> a              | and V <sub>DD</sub> )                |

| Output voltage                                             | $V_{SS} - 0.3$ V to $V_{DD} + 0.3$ V |

| (any output pin to its local V <sub>ss</sub>               | and V <sub>DD</sub> )                |

| Storage temperature                                        | – 55 °C to + 150 °C                  |

| Operating temperature                                      | – 40 °C to + 85 °C                   |

These are not the operating conditions, but are the absolute limits which if exceeded even momentarily may cause permanent damage. To ensure sustained correct operation the device should be used within the limits given under Electrical Characteristics.

To avoid any possibility of latch-up the substrate connec-

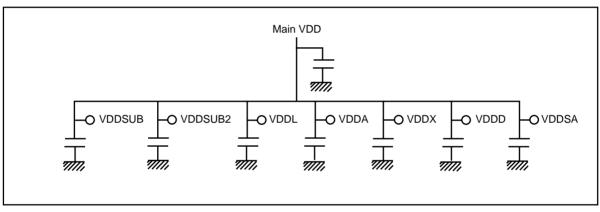

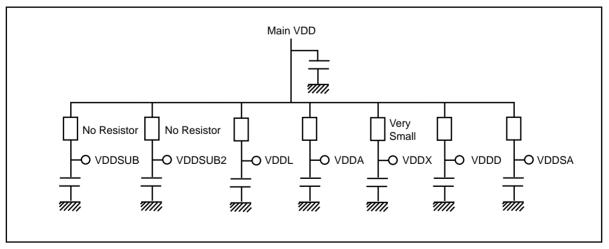

tions  $V_{\mbox{\tiny DDSUB}}$  and  $V_{\mbox{\tiny DDSUB2}}$  must be the most positive of all  $V_{\mbox{\tiny DD}}$  's at all times including during power on and off ramping. As the current taken through these  $V_{\text{DD}}$ 's is significantly less than through the other  $V_{DD}$ 's this requirement can be easily met by directly connecting all  $V_{DD}$  pins to a common point on the circuit board but with the decoupling capacitors distributed to minimise cross-talk caused by common mode currents. If low value series resistors are to be included in the  $V_{\mbox{\tiny DD}}$  connections, with decoupling capacitors by the ACE9030 pins to further reduce interference, the  $V_{\text{DDSUB}}$  and  $V_{\text{DDSUB2}}$  pins should not have such a resistor in order to guarantee that their voltage is not slowed down at power-on. Power switches to DOUT0 and DOUT1 are supplied from  $V_{\mbox{\tiny DDX}}$  and are specified for a total current of up to 40 mA so any resistor in the V<sub>DDX</sub> connection must be very low, around  $1\Omega$ , in order to avoid excessive voltage drop; it is recommended that this supply has no series resistor. These two methods are shown in circuit diagrams, figures 4 and 5. In both circuits the main  $V_{DD}$  must also have good decoupling.

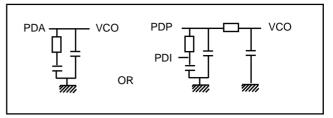

Fig.4 Typical VDD local decoupling networks without series resistors

Fig.5 Typical VDD local decoupling networks with series resistors

# **ELECTRICAL CHARACTERISTICS**

These characteristics apply over these ranges of conditions (unless otherwise stated):  $T_{AMB} = -40 \text{ °C to} + 85 \text{ °C}, V_{DD} = +3.6 \text{ to} + 5.0 \text{ V}, \text{ GND ref.} = V_{SS}$

#### D.C. Characteristics

| Parameter                                         | Min.                   | Тур. | Max.                     | Unit | Conditions                       |

|---------------------------------------------------|------------------------|------|--------------------------|------|----------------------------------|

| Power supply                                      |                        | •    |                          | •    |                                  |

| Supply current, Radio Interface:                  |                        |      |                          |      |                                  |

| Sleep mode                                        |                        | 2.3  | 2.7                      | mA   | XO, OSC8 on                      |

| Fully operating (excluding I <sub>DDX</sub> )     |                        |      | 7                        | mA   | (see Note 1)                     |

| Supply current, Synthesisers: V <sub>DD</sub> =5V |                        |      |                          |      | $f_{REF} = 10 \text{ MHz}$       |

| Main and Auxiliary ON                             |                        |      | 5                        | mA   | f <sub>MAIN</sub> = 10 MHz       |

| Main ON and Auxiliary in Standby                  |                        |      | 3.7                      | mA   | $f_{AUX} = 10 \text{ MHz}$       |

| Main in Standby and Auxiliary ON                  |                        |      | 3                        | mA   | (see Note 2)                     |

| Main and Auxiliary in Standby, with Bandgap off   |                        |      | 100                      | μA   |                                  |

| Supply current, Synthesisers:                     |                        |      |                          |      | f <sub>REF</sub> = 15 MHz        |

| Main and Auxiliary ON                             |                        | 3    |                          | mA   | f <sub>MAIN</sub> = 16 MHz       |

| Main ON and Auxiliary in Standby                  |                        | 2    |                          | mA   | $f_{AUX} = 90 \text{ MHz}$       |

| Main in Standby and Auxiliary ON                  |                        | 2    |                          | mA   | (see Note 2)                     |

| Main and Auxiliary in Standby                     |                        |      | 100                      | μA   |                                  |

| Input and output signals                          |                        |      |                          |      |                                  |

| Logic input HIGH (LATCHC, LATCHB, DATA,           |                        |      |                          |      |                                  |

| CL, and TEST)                                     | 0.7 x V <sub>DD</sub>  |      | V <sub>DD</sub> + 0·3    | V    |                                  |

| Logic input LOW (LATCHC, LATCHB, DATA,            |                        |      |                          |      |                                  |

| CL, and TEST)                                     | - 0.3                  |      | + 0.8                    | V    |                                  |

| Input capacitance (signal pins)                   |                        |      | 10                       | pF   | Pin voltage                      |

| Input leakage (signal pins)                       |                        |      | 1                        | μA   | $V_{ss}$ to $V_{DD}$             |

| Logic output HIGH (RXCD, DATA, AFCOUT,            | $V_{DD} - 0.5$         |      |                          | V    |                                  |

| TEST and DOUT2, 3 and 4)                          |                        |      |                          |      | External load:                   |

| Logic output LOW (RXCD, DATA, AFCOUT,             |                        |      | 0.4                      | V    | 20 kΩ & 30 pF                    |

| TEST and DOUT2, 3 and 4)                          |                        |      |                          |      |                                  |

| Output ON level, DOUT0 and DOUT1                  | V <sub>DDX</sub> - 0.2 |      |                          | V    | I <sub>он</sub> = 20 mA.         |

| Output HIGH level, DOUT5, 6 and 7                 | 2.3                    |      | 2.9                      | V    | I <sub>OH</sub> = 80 μA          |

| Output LOW level, DOUT5, 6 and 7                  |                        |      | 0.3                      | V    | I <sub>OL</sub> = 0.2 μA         |

| Trimmed output level ON, DOUT8                    | 3.35                   |      | 3.55                     | V    | I <sub>OH</sub> = 135 to 400 μA. |

| Level difference, DOUT8 ON – ADC reference        | - 5                    |      | + 15                     | mV   |                                  |

| Output level OFF, DOUT8                           |                        |      | 0.4                      | V    |                                  |

| MODMP, MODMN output HIGH                          | $V_{DD}/2 + 0.35$      |      | V <sub>DD</sub> /2 + 1.0 | V    | I <sub>OH</sub> = 10 μA          |

| MODMP, MODMN output LOW                           | $V_{DD}/2 - 1.0$       |      | $V_{DD}/2 - 0.35$        | V    | I <sub>oL</sub> = - 10 μA        |

| Input Schmitt Hysteresis, pins CL, LATCHB,        | 0.3                    |      |                          | V    |                                  |

| LATCHC, DATA.                                     |                        |      |                          |      |                                  |

| Analog circuits bias resistor on IREF             |                        | 68   |                          | kΩ   | V <sub>DD</sub> @ 3.75 V         |

|                                                   |                        | 100  |                          | kΩ   | V <sub>DD</sub> @ 4.85 V         |

Notes

1. The sleep current is specified with the crystal oscillator (XO) and the OSC8 oscillator and PLL running as these are normally needed to provide the clock to the system controller.

The terms f<sub>REF</sub>, f<sub>MAIN</sub>, and f<sub>AUX</sub> refer to the frequencies of the Reference inputs (Crystal oscillator, pins CIN1 and CIN2), the Main synthesiser inputs (pins FIM and FIMB) and the Auxiliary synthesiser inputs (pins FIA and FIAB) respectively.

## **ELECTRICAL CHARACTERISTICS**

These characteristics apply over these ranges of conditions (unless otherwise stated):  $T_{AMB} = -40$  °C to + 85 °C,  $V_{DD} = +3.6$  to + 5.0 V, GND ref. =  $V_{SS}$

#### **D.C. Characteristics (continued)**

| Parameter                                                               | Min. | Тур. | Max. | Unit | Conditions                    |

|-------------------------------------------------------------------------|------|------|------|------|-------------------------------|

| Synthesiser charge pump current                                         |      |      |      |      |                               |

| Current setting resistor R <sub>SMA</sub>                               | 19   | 39   | 78   | kΩ   | Note 3                        |

| Current setting resistor R <sub>sc</sub>                                | 19   | 39   | 78   | kΩ   | Note 3                        |

| External capacitance on pin R <sub>SMA</sub>                            |      |      | 5    | pF   | Ensures stable                |

| External capacitance on pin R <sub>sc</sub>                             |      |      | 5    | pF   | bias current.                 |

| Bias current I <sub>RSMA</sub> (nominally 1.25V / R <sub>SMA</sub> )    | 28.8 | 32   | 35-2 | μA   | R <sub>SMA</sub> = 39 kΩ      |

| Bias current I <sub>RSC</sub> (nominally 1.25V / R <sub>SC</sub> )      | 28.8 | 32   | 35-2 | μΑ   | $R_{sc} = 39 \text{ k}\Omega$ |

| Iprop(0) scaling accuracy, pin PDP                                      | -10  |      | +10  | %    | @ 200 μA. Note 4              |

| Iprop(1) scaling accuracy, pin PDP                                      | -10  |      | +10  | %    | @ 800 µA. Note 4              |

| lint scaling accuracy, pin PDI                                          | -10  |      | +10  | %    | @ 4 mA. Note 4                |

| Icomp(0) scaling accuracy, pin PDP                                      | -10  |      | +10  | %    | @ ACC x 0·2 μA                |

|                                                                         |      |      |      |      | Note 4                        |

| Icomp(1) scaling accuracy, pin PDP                                      | -10  |      | +10  | %    | @ ACC x 0·8 μA                |

|                                                                         |      |      |      |      | Note 4                        |

| Icomp(2) scaling accuracy, pin PDI                                      | -10  |      | +10  | %    | @ ACC x 4 μA                  |

|                                                                         |      |      |      |      | Note 4                        |

| lauxil scaling accuracy, pin PDA                                        | -5   |      | +5   | %    | @ 256 μA. Note 4              |

| Auxiliary Charge Pump,                                                  | -10  |      | +10  | %    | Note 5                        |

| Up or Down I <sub>AUX</sub> current variation                           |      |      |      |      |                               |

| Main Charge Pumps,                                                      | -10  |      | +10  | %    | Note 6                        |

| Up or Down I <sub>MAIN</sub> or I <sub>INTEGRAL</sub> current variation |      |      |      |      |                               |

| Iprop(0) or Iprop(1) setting from PDP pin                               |      |      | 1.0  | mA   |                               |

| lint setting from PDI pin                                               |      |      | 5    | mA   |                               |

| Icomp(0) or Icomp(1) setting from PDP pin                               |      |      | 12   | μA   |                               |

| Icomp(2) setting from PDI pin                                           |      |      | 180  | μA   |                               |

| lauxil setting from PDA pin                                             |      |      | 512  | μA   |                               |

Notes

3. The circuit is defined with resistors  $R_{SMA}$  and  $R_{SC}$  connected from pins RSMA and RSC to  $V_{SSSA}$  but in most practical applications all  $V_{SS}$  pins will be connected to a ground plane so  $R_{SMA}$  and  $R_{SC}$  should then also be connected to this ground plane.

- 4. The charge pump currents are specified to this accuracy when the relevant output pin is at a potential of  $V_{DD}/2$  and with  $R_{SMA} = 39 \text{ k}\Omega$ , CN = 200, L=1, K=5, R<sub>sc</sub> = 19 kΩ. The nominal value is set by external resistors and by programming registers, as defined in Table 6. Tolerances in the internal Bandgap voltage and bias circuits are within the limits given for I<sub>RSMA</sub> and I<sub>RSC</sub>, the scaling accuracy of the multiplying DAC's is within these limits given for lprop(0), lprop(1), lint, lcomp(0), lcomp(1), lcomp(2), and auxil.

- 5. The Auxiliary charge pump output voltage is referred to as V<sub>PDA</sub> and the output current I<sub>AUX</sub> is the Up or Down current measured when  $V_{PDA} = V_{DD}/2$ .

| The cond | litions for the variation lim    | its for th | ne Up current are:                                              |

|----------|----------------------------------|------------|-----------------------------------------------------------------|

| either   | I <sub>AUX</sub> = 128 or 256 μA | and        | $0 < V_{PDA} < V_{DD} - 0.5 V$                                  |

| or       | I <sub>AUX</sub> = 512 μA        |            | $0 < V_{PDA} < V_{DD} - 0.65 V$                                 |

| The cond | litions for the variation lim    | its for th | ne Down current are:                                            |

| either   | I <sub>AUX</sub> = 128 or 256 μA |            |                                                                 |

| or       | $I_{AUX} = 512 \ \mu A$          | and        | $0.65 \text{ V} < \text{V}_{\text{PDA}} < \text{V}_{\text{DD}}$ |

6. The Main charge pump output voltage at pin PDP is referred to as V<sub>PDP</sub> and at pin PDI as V<sub>PDI</sub>. The output currents I<sub>MAIN</sub> and I<sub>INTEGRAL</sub> are the up or down current lprop(0), lprop(1) or lint measured when  $V_{PDP}$  or  $V_{DPI} = V_{DD}/2$ . The conditions for the variation limits for the Up current are :

$I_{MAIN} = 100$  to  $1000 \ \mu\text{A}$  or  $I_{INTEGRAL} = 1$  to 5 mA and  $0 < V_{PDP} < V_{DD} - 0.45 \text{ V}$ The conditions for the variation limits for the Down current are:

$I_{_{MAIN}}$  = 100 to 1000  $\mu A\,$  or  $\,I_{_{INTEGRAL}}$  = 1 to 5 mA and  $\,$  0.45 V <  $V_{_{PDP}}$  <  $V_{_{DD}}$

ELECTRICAL CHARACTERISTICS These characteristics apply over these ranges of conditions (unless otherwise stated):  $T_{AMB} = -40 \text{ °C}$  to +85 °C,  $V_{DD} = +3.6$  to +5.0 V, GND ref. =  $V_{SS}$

# A.C. Characteristics

| Parameter                                                                 | Min.  | Тур. | Max.  | Unit              | Conditions                               |

|---------------------------------------------------------------------------|-------|------|-------|-------------------|------------------------------------------|

| CONTROL BUS                                                               |       |      |       |                   |                                          |

| Clock rate CL input                                                       |       | 1008 |       | kHz               |                                          |

| Clock duty cycle CL input                                                 | 40    | 50   | 60    | %                 |                                          |

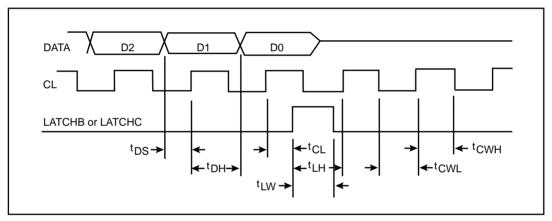

| t <sub>DS</sub> , input data set-up time                                  | 80    |      |       | ns                | See Fig. 7                               |

| t <sub>DH</sub> , input data hold time                                    | 80    |      |       | ns                | See Fig. 7                               |

| t <sub>CWL</sub> , t <sub>CWH</sub> , CL input pulse width (to bus logic) | 400   |      | 600   | ns                | See Fig. 7                               |

| t <sub>cL</sub> , delay time, clock to latch                              | 440   |      |       | ns                | See Fig. 7                               |

| t <sub>LW</sub> , latch pulse high time                                   | 230   |      |       | ns                | See Fig. 7                               |

| t <sub>LH</sub> , delay time, latch to clock                              | 220   |      |       | ns                | See Fig. 7                               |

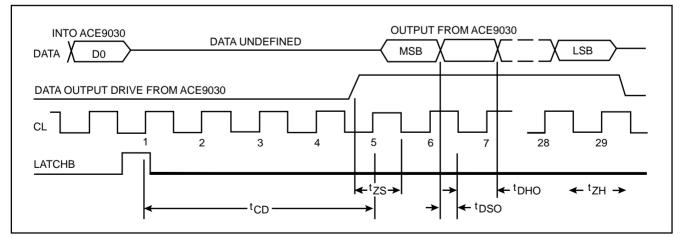

| t <sub>DSO</sub> , output data set-up time                                | 80    |      |       | ns                | See Fig. 8                               |

| t <sub>DHO</sub> , output data hold time                                  | 80    |      |       | ns                | See Fig. 8                               |

| t <sub>zs</sub> , DATA line available to ACE9030                          | 80    |      | 1200  | ns                | See Fig. 8                               |

| t <sub>ZH</sub> , DATA line released by ACE9030                           | 80    |      | 1200  | ns                | See Fig. 8                               |

| t <sub>CD</sub> , delay from received message to                          | 4     |      | 4     | cycles            | See Figs. 8 and 10                       |

| transmitted response                                                      |       |      |       | of CL             | Ū                                        |

| Rise and Fall times, all digital inputs:                                  |       |      | 50    | ns                |                                          |

| DIGITAL OUTPUTS                                                           |       |      |       |                   |                                          |

| DOUT0 and 1 On time to $V_{DD} - 0.2 V$                                   |       |      | 100   | μs                | 100 nF load and from                     |

| DOUT0 and 1 Off time to > 1 M $\Omega$                                    |       |      | 100   | μs                | LATCHB rising edge                       |

| DOUT5, 6 and 7 rise and fall times                                        |       |      | 10    | μs                | 30 pF load and to D.C                    |

| DOUT8 rise and fall time                                                  |       |      | 10    | μs                | specification noise                      |

| A to D CONVERTER                                                          | 1     | I    | -     |                   |                                          |

| Lowest transition, 0000 0000 to 0000 0001                                 | 0.07  | 0.15 | 0.23  | V                 | Bandgap multiplier                       |

| Highest transition, 1111 1110 to 1111 1111                                | 3.35  | 3.45 | 3.55  | V                 | correctly trimmed                        |

| ADC conversion time (20 cycles of CL)                                     |       | 20   |       | μs                | CL = 1008 kHz                            |

| Input scanning rate (CL ÷ 40)                                             |       | 25.2 |       | ,<br>kHz          | CL = 1008 kHz                            |

| Integral Non-linearity                                                    | - 1   |      | + 1   | LSB               |                                          |

| Differential Non-linearity                                                | - 0.8 |      | + 0.8 | LSB               |                                          |

| Power supply sensitivity                                                  |       |      | 3     | LSB/0.3V          | 0 to 10 kHz                              |

| CRYSTAL OSCILLATOR                                                        |       |      | -     |                   |                                          |

| Start-up time of crystal oscillator                                       |       |      | 5     | ms                |                                          |

| Crystal effective series resistance (ESR)                                 |       |      | 25    | Ω                 |                                          |

| Power dissipation in crystal                                              |       | 50   | 150   | μW                |                                          |

| D to A CONVERTERS                                                         |       |      | 100   | μ                 |                                          |

| Full scale output level, DAC1, DAC2 & DAC3                                | 3.35  | 3.45 | 3.55  | V                 | Bandgap multiplier                       |

| Zero scale output level, DAC1                                             | 1.0   | 0.0  | 1.2   | V                 | trimmed to nominal                       |

| Zero scale output level, DAC2 & DAC3                                      | 0.3   |      | 0.5   | V                 | reference voltage                        |

| Integral Non-linearity                                                    | - 1   |      | + 1   | LSB               | i ci |

| Differential Non-linearity                                                | - 0.5 |      | + 0.5 | LSB               |                                          |

| Output wideband and clock noise:                                          |       |      |       |                   |                                          |

| 50 Hz to 1.1 MHz, flat integration                                        |       |      | 3     | mV <sub>rms</sub> |                                          |

| Power supply rejection ratio                                              | 30    |      | 0     | dB                | 50 Hz to 25 kHz.                         |

| Settling time to within 10% of end of step                                |       |      | 6     | μs                | DAC1 and DAC2                            |

| (DAC3 with external 15 k $\Omega$ resistor)                               |       |      | 0     | μο                | 10 pF load                               |

| Output load capacitance, DAC1 and DAC2                                    |       |      | 100   | nF                |                                          |

| Output load capacitance, DAC3                                             |       |      | 30    | pF                | To guarantee stability                   |

|                                                                           |       |      | 50    | Pi                | To guarantee stability                   |

| Internal series resistor, DAC1 and DAC2                                   | 7     | 15   | 40    | kΩ                |                                          |

# **ELECTRICAL CHARACTERISTICS**

These characteristics apply over these ranges of conditions (unless otherwise stated):  $T_{AMB} = -40 \text{ °C to} + 85 \text{ °C}$ , all  $V_{DD} = +3.6 \text{ to} + 5.0 \text{ V}$ , GND ref. =  $V_{SS}$

# A.C. Characteristics (continued)

| Parameter                                      | Min.                   | Тур.  | Max.             | Unit               | Conditions            |

|------------------------------------------------|------------------------|-------|------------------|--------------------|-----------------------|

| LOW FREQUENCY AMPLIFIERS (1 and 2)             |                        |       |                  |                    |                       |

| Voltage Gain                                   | 1200                   | 2800  |                  |                    |                       |

| Input Offset                                   |                        | 10    | 20               | mV                 |                       |

| Open loop input resistance                     |                        | 1     |                  | MΩ                 |                       |

| Open loop output resistance                    |                        | 8     |                  | kΩ                 |                       |

| Unity Gain bandwidth                           |                        | 2     |                  | MHz                |                       |

| Input bias current, inverting input            |                        |       | 200              | nA                 |                       |

| Power supply rejection at 120 Hz, 10 kHz       | 40                     | 50    |                  | dB                 |                       |

| Output voltage maximum                         | V <sub>DDA</sub> - 0.2 |       |                  | V                  | 10 kΩ to 6ND          |

| Output voltage maximum, as a comparator        | V <sub>DDA</sub> - 0.1 |       |                  | V                  | 10 kΩ to 6ND          |

| Output voltage minimum level                   |                        |       | 0.2              | V                  | 10 kΩ to 6ND          |

| Output voltage minimum level                   |                        |       | 0.1              | V                  | 10 kΩ to 6ND          |

| Common mode input range (LF1 1)                | V <sub>SSA</sub>       |       | 2.5              | V                  |                       |

| Common mode input range (LF1 2)                | V <sub>SSA</sub>       |       | $V_{\text{DDA}}$ |                    |                       |

| Output slew rate                               | 0.15                   | 0.25  |                  | V/µs               |                       |

| Output load capacitance                        |                        |       | 30               | pF                 |                       |

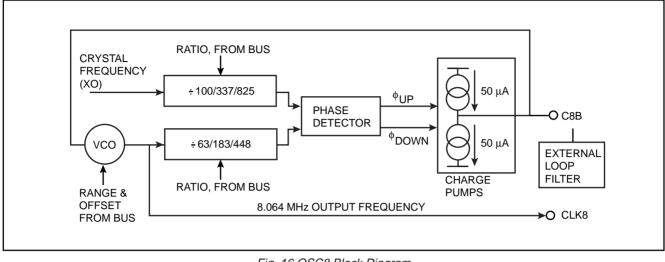

| 8 MHz OSCILLATOR and PLL                       |                        |       |                  |                    |                       |

| OSC8 centre frequency                          |                        | 8.064 |                  | MHz                |                       |

| OSC8 VCO sensitivity                           |                        | 25    |                  | MHz/V              |                       |

| OSC8 charge pump output current                |                        | 50    |                  | μA                 |                       |

| CLK8 output load, resistive:                   | 15                     | 25    | 100              | kΩ                 |                       |

| capacitive:                                    | 15                     | 25    | 30               | pF                 |                       |

| CLK8 output amplitude                          | 0-8                    | 1.0   | 2.4              | V <sub>pk-pk</sub> |                       |

| CLK8 total output jitter                       |                        |       | 500              | Hz                 | 0 - 3 kHz             |

| Start-up time at power-on, to default settings |                        |       | 15               | ms                 | With a loop filter as |

|                                                |                        |       |                  |                    | described in fig. 17  |

| Lock time to within 125 ppm, after             |                        |       |                  |                    |                       |

| reprogramming set-ups                          |                        |       | 15               | ms                 |                       |

| AFCIN F.M. DISCRIMINATOR and AFC               |                        |       |                  |                    |                       |

| AFCIN input signal level                       | 0.05                   |       | 2.5              | V <sub>pk-pk</sub> |                       |

| AFCIN input impedance, resistive:              | 50                     |       |                  | kΩ                 |                       |

| capacitive:                                    |                        |       | 10               | pF                 |                       |

| Input frequency                                | 400                    |       | 500              | kHz                |                       |

| Input signal to integrated noise ratio         | 10                     |       |                  | dB                 | I.F. ± 15 kHz.        |

| Input Schmitt Hysteresis                       | 8                      |       |                  | mV                 |                       |

| AUDIO signal SINAD, psophometric, note 7       | 40                     | 45    |                  | dB                 | 1 kHz tone at 3 kHz   |

| AUDIO signal hum and noise, note 7             |                        |       | - 46             | dB                 | peak deviation on     |

| AUDIO output signal level, note 7              | 195                    | 260   |                  | mV <sub>rms</sub>  | AFCIN input at I.F.   |

| AFCOUT load                                    |                        |       | 30               | pF                 |                       |

| AFCOUT duty cycle                              | 37                     |       | 63               | %                  |                       |

| AFCOUT rise and fall times                     |                        |       | 75               | ns                 |                       |

Note

<sup>7.</sup> AUDIO signal quality is measured with feedback components as shown in figure 18 and with 500 mV peak to peak input to AFCIN. Discriminator gain is set with D = 3 and M = 40 and  $V_{DD}$  = 3.75 V and a crystal at 14.85 MHz. SINAD is defined as the ratio of wanted signal to all unwanted output, measured simultaneously with filters. The hum and noise figure is defined as the ratio of output power at AUDIO when AFCIN is unmodulated to the output power when AFCIN is driven as specified above.

# **ELECTRICAL CHARACTERISTICS**

These characteristics apply over these ranges of conditions (unless otherwise stated):  $T_{AMB} = -40$  °C to + 85 °C, all  $V_{DD} = +3.6$  to + 5.0 V, GND ref. =  $V_{SS}$

# A.C. Characteristics (continued)

| Parameter                                      | Min.                  | Тур. | Max.                   | Unit                | Conditions                             |

|------------------------------------------------|-----------------------|------|------------------------|---------------------|----------------------------------------|

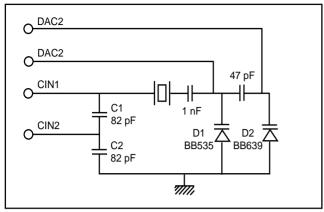

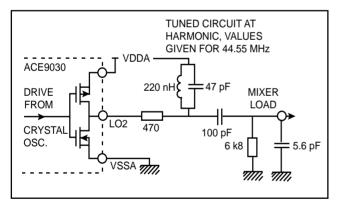

| LO2 Multiplier                                 | 4                     |      | 1                      |                     |                                        |

| Amplitude                                      | 235                   |      | 500                    | mV <sub>rms</sub>   | Circuit as in fig. 15,                 |

| Reference frequency content of output          |                       |      | -10.5                  | dBc                 |                                        |

| 2nd, 4th harmonic content of output            |                       |      | -13.5                  | dBc                 |                                        |

| 5th harmonic of output                         |                       |      | -15                    | dBc                 |                                        |

| 6th and higher harmonics in output             |                       |      | -20                    | dBc                 |                                        |

| SYNTHESISERS                                   |                       |      |                        |                     | 1                                      |

| Reference divider                              |                       |      |                        |                     |                                        |

| Reference divider input frequency              | 5                     |      | 30                     | MHz                 |                                        |

| Drive level into CIN1 from external oscillator | 400                   |      |                        | mV <sub>pk-pk</sub> | With crystal oscillato<br>powered down |

| CIN1 input capacitance                         |                       |      | 10                     | pF                  |                                        |

| CIN1 input resistance                          | 10                    |      |                        | kΩ                  |                                        |

| Auxiliary synthesiser                          |                       |      |                        |                     |                                        |

| FIA input frequency                            | 10                    |      | 135                    | MHz                 | May be a sinewave                      |

| Rise and fall times of inputs                  |                       |      | 10                     | ns                  |                                        |

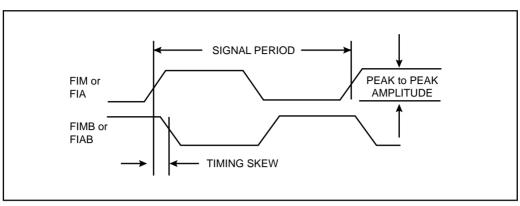

| Timing Skew between FIA and FIAB               |                       |      | ± 2                    | ns                  | See Fig. 6                             |

|                                                |                       |      | or ± 10%               | signal              | Both maxima                            |

|                                                |                       |      |                        |                     | must be met                            |

| FIA, FIAB differential signal level with both  | 180                   |      |                        | mV <sub>pk-pk</sub> | Each input, 5 to 50 8                  |

| sides driven                                   |                       |      |                        |                     | 99 to 135 MHz                          |

|                                                | 100                   |      |                        | mV <sub>pk-pk</sub> | Each input,                            |

|                                                |                       |      |                        |                     | 50 to 99 MHz                           |

| FIA single input drive level with FIAB         | 360                   |      |                        | mV <sub>pk-pk</sub> | One input, 5 to 50 &                   |

| decoupled to V <sub>ss</sub>                   |                       |      |                        |                     | 99 to 135 MHz                          |

|                                                | 200                   |      |                        | mV <sub>pk-pk</sub> | One input,                             |

|                                                |                       |      |                        |                     | 50 to 99 MHz                           |

| FIA, FIAB common mode range                    | V <sub>DD</sub> – 1.7 |      | $V_{DD} - 0.7$         | V                   | $V_{DD} = 3.6V$                        |

| FIA, FIAB common mode range                    | 2.8                   |      | V <sub>DD</sub> - 0.85 | V                   | $V_{DD} = 5V$                          |

| FIA, FIAB input capacitance                    |                       |      | 10                     | pF                  |                                        |

| FIA, FIAB differential input resistance        | 10                    |      |                        | kΩ                  | Note 8                                 |

| Auxiliary Synthesiser comparison frequency     |                       |      | 2                      | MHz                 |                                        |

| Main Synthesiser                               | +                     |      |                        |                     |                                        |

| FIM input frequency                            | 4                     |      | 20                     | MHz                 |                                        |

| Rise and fall times of inputs                  |                       |      | 50                     | ns                  |                                        |

| FIM - FIMB Timing Skew                         |                       |      | ± 2                    | ns                  | See Fig. 6                             |

|                                                |                       |      | or ± 10%               | signal              | Both maxima                            |

|                                                |                       |      |                        | period              | must be met                            |

| FIM, FIMB differential signal level            | 100                   |      |                        | mV <sub>pk-pk</sub> | Each input,                            |

| with both sides driven.                        |                       |      |                        |                     | 4 to 20 MHz                            |

| FIM single input drive level                   | 200                   |      | 1000                   | mV <sub>pk-pk</sub> | One input,                             |

| with FIMB decoupled to V <sub>ss</sub>         |                       |      |                        |                     | 4 to 20 MHz                            |

| FIM, FIMB common mode range                    | V <sub>DD</sub> – 1.7 |      | $V_{DD} - 0.7$         | V                   | V <sub>DD</sub> =3.6V                  |

| FIM, FIMB common mode range                    | 2.8                   |      | V <sub>DD</sub> - 0.85 | V                   | V <sub>DD</sub> =5V                    |

| FIM, FIMB input capacitance                    |                       |      | 10                     | pF                  |                                        |

| FIM, FIMB differential input resistance        | 10                    |      |                        | kΩ                  | Note 8                                 |

| Delay FIM rising to MODMP/MODMN changing       |                       |      | 30                     | ns                  |                                        |

| Main Synthesiser comparison frequency          | 1                     | 1    | 2                      | MHz                 |                                        |

Note

To simplify single ended drive there is a resistor between FIA and FIAB and another between FIM and FIMB. In this mode the inputs should drive FIA or FIM with D.C. coupling and the other inputs FIAB and FIMB should be decoupled to ground by external capacitors.

# TIMING WAVEFORMS

Fig. 6 Synthesiser Inputs

Fig. 7 Control Bus input timing

Fig. 8 Control Bus output timing

# **FUNCTIONAL DESCRIPTION - CONTROL BUS**

The functions of the ACE9030 fall into two separate groups, the Radio Interface and the Synthesisers.

The common control bus splits the input strings differently for these two sections so this bus operation is described first as an introduction to the available features.

All functions are controlled by a serial bus; DATA is a bidirectional data line, to input all control data and to output the results of measurements in the Radio Interface section, CL is the clock, and LATCHB and LATCHC are the latch signals at the end of each control word for either the Radio Interface or the Synthesiser section respectively.

CL is a continuously running clock at typically 1.008 MHz, and all incoming and output data are latched on rising edges of this clock. The controller should clock data in and out on falling clock edges. For bus control purposes the frequency of CL may be widely varied and this clock does not need to be continuous, however, the sampled I.F. signal AFCOUT, the Polling ADC, and the Lock Detect Filter also use CL as the sampling clock. In systems where any of these are required the clock CL is constrained to be 1.008 MHz and to be continuous.

To ensure clean initialisation the clock CL should give at least 8 cycles before the power-up command and similarly to set the control logic to known states there should be 8 cycles of CL after a power-down command.

During normal operation there should be at least 30 cycles of CL between latch pulses, 24 for the data bits (see figures 9,10 & 11) plus 6 extra. This minimum becomes 36 cycles if the extended synthesiser programming command (A2) is used.

# **Radio Interface Bus - Receive**

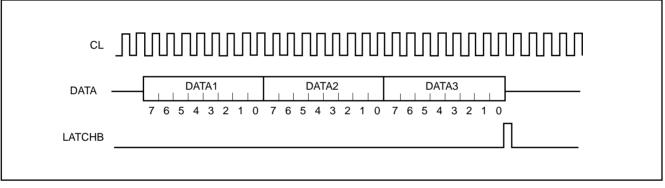

#### Fig.9 Radio Interface receive bus timing

The received data is split into three bytes, where DATA1 normally contains a value to be loaded into a destination set by DATA2 and DATA3. When a command does not need to put any information into byte DATA1 a preamble xx1010xx is recommended to fill this byte. It is possible to set-up several features in one bus operation and to allow this the decoding only acts on single or selected bits; the others are given as "x" in the block descriptions. Two bits of DATA2 also set the type of command, with four options:

| DATA2 | DATA2 | Type of | Comment             |

|-------|-------|---------|---------------------|

| bit 7 | bit 6 | Command |                     |

| 0     | 0     | SLEEP   | No reply            |

| 0     | 1     | NORMAL  | Send requested data |

| 1     | 0     | SET-UP  | No reply            |

| 1     | 1     | TEST    | No reply            |

Sleep mode is selected to put the cellular terminal into a very low power state for when it is "Off" and neither waiting for, nor setting up a call. In Sleep only the crystal and 8.064 MHz oscillators, DAC1 and DAC2, the OSC8 phase locked loop,

and the CLK8 output driver will be active, and are used to clock the microcontroller. To reduce the supply current to its minimum in Sleep the synthesisers must also be powered down, by a Word D message with DA and DM both set HIGH as described under **Synthesiser Bus - Receive Only**. During Sleep all set-up values are retained unless changed by a Setup command. The exit from Sleep is by any Normal command.

Normal commands will end Sleep mode but are primarily used to change the operating mode of the cellular terminal or to request ADC data. The ACE9030 will output data onto the serial bus after a Normal command.

Set-up commands are used to adjust various operating parameters but can also initiate a logic restart if DATA3 bits 1 and 0 are both "1" so for routine changes of set-ups these bits should always be 00.

Test mode is included only for use during chip manufacture.

## The Sleep Command - DATA2 bits 7, 6 = 00

| DATA1    | DATA2    | DATA3    |

|----------|----------|----------|

| xx1010xx | 00xxxxxx | XXXXXXXX |

# Summary of Normal Commands - DATA2 bits 7, 6 = 01

Normal commands are always a request for data; the ADC registers to be read are defined by Y1 and Y0 in DATA3. A normal command will also end Sleep mode.

| BIT    | EFFECT when at 0                                     | EFFECT when at 1                                     |  |  |

|--------|------------------------------------------------------|------------------------------------------------------|--|--|

| DATA2: |                                                      |                                                      |  |  |

| 7      | With DATA2:6 defines command type                    | -                                                    |  |  |

| 6      | -                                                    | With DATA2:7 defines command type                    |  |  |

| 5      | Discriminator powered down                           | Discriminator active.                                |  |  |

| 4      | -                                                    | Load Lock threshold register from DATA1:7-1          |  |  |

| 3      | DAC3 powered down                                    | DAC3 active                                          |  |  |

| 2      | -                                                    | Load DOUT7-0 from DATA1:7-0                          |  |  |

| 1      | -                                                    | Load DAC3 from DATA1:7-0                             |  |  |

| 0      | Not used                                             | Not used                                             |  |  |

| DATA3: |                                                      |                                                      |  |  |

| 7      | Not used                                             | Not used                                             |  |  |

| 6      | LO2 multiplier powered down                          | LO2 multiplier active                                |  |  |

| 5      | Set DOUT8 to OFF                                     | Set DOUT8 to ON, to output the ADC reference voltage |  |  |

| 4      | -                                                    | Load ADC1 comparator from DATA1:7-0                  |  |  |

| 3      | -                                                    | Load DAC1 from DATA1:7-0                             |  |  |

| 2      | - Load DAC2 from DATA1:7-0                           |                                                      |  |  |

| 1      | Y1 Decode with DATA3:0 for Polling ADC register read |                                                      |  |  |

| 0      | Y0 Decode with DATA                                  | Y0 Decode with DATA3:1 for Polling ADC register read |  |  |

# Summary of Set-up Commands - DATA2 bits 7, 6 = 10

| BIT    | EFFECT when at 0                     | EFFECT when at 1                                 |

|--------|--------------------------------------|--------------------------------------------------|

| DATA2: |                                      |                                                  |

| 7      | -                                    | With DATA2:6 defines command type                |

| 6      | With DATA2:7 defines command type    | -                                                |

| 5      | Not used                             | Not used                                         |

| 4      | -                                    | Set OSC8 VCO range from DATA1:5-0                |

| 3      | -                                    | Set OSC8 VCO offset from DATA1:5-0               |

| 2      | Select input A for ADC3              | Select input B for ADC3                          |

| 1      | Select input A for ADC2              | Select input B for ADC2                          |

| 0      | OSC8 off                             | OSC8 on                                          |

| DATA3: |                                      |                                                  |

| 7      | Crystal oscillator off               | Crystal oscillator on                            |

| 6      | Bandgap off - use external reference | Bandgap on                                       |

| 5      | -                                    | Set discriminator divisors from DATA1:7,6        |

|        |                                      | and lock detect period from DATA1:5              |

|        |                                      | and OSC8 divisors from DATA1:2-0                 |

| 4      | -                                    | Set bandgap trim from DATA1:7-0                  |

| 3      | Not used                             | Not used                                         |

| 2      | Not used                             | Not used                                         |

| 1      | -                                    | Do a restart if both DATA3 bits 1 and 0 are at 1 |

| 0      | -                                    | Do a restart if both DATA3 bits 1 and 0 are at 1 |

# **Radio Interface Bus - Transmit**

The ACE9030 only drives the bus in response to a request for data by a Normal command as described above. To avoid any bus contention, there is a delay from the end of a data request to the start of the response, see figure 10. The data will start on the fifth rising edge of CL after the rising edge of LATCHB. The output Preamble word begins with a fixed pattern 1 0 1 0 and then includes the source code number (Y1, Y0) for the Result words and the status of the Lock Detect from the synthesiser, all as described in the section Polling A to D Converter.

Fig.10 Radio Interface transmit bus timing

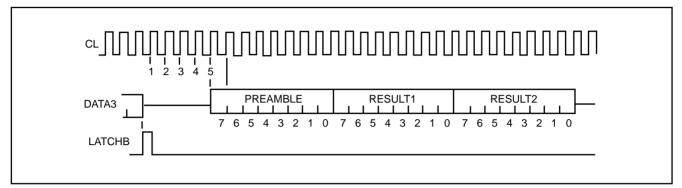

# Synthesiser Bus - Receive Only

The overall format to control the synthesiser is basically the same as for the Radio Interface. There is an option of a 32 bit

sequence for the A word. The width of the LATCHC pulse is used to set the duration of speed-up mode when changing channels.

Fig.11 Synthesiser bus timing

Data is accepted by the circuit on the rising edge of LATCHC. Programmable divider ratios will be changed at their next re-load, at up to a whole comparison period after the LATCHC edge.

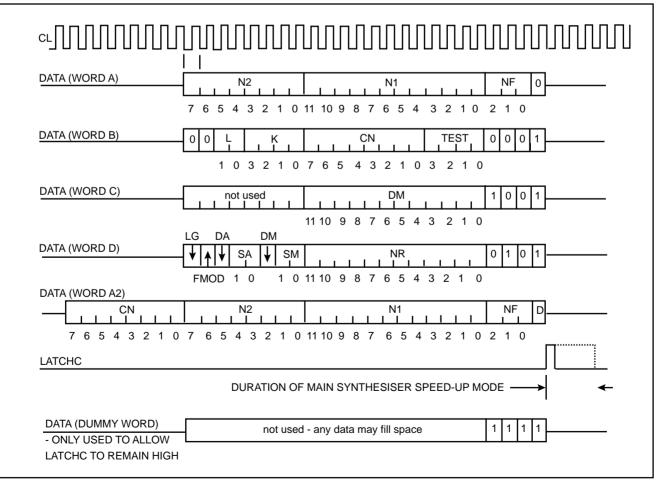

Normal channel changes require only word A but if it is necessary to maintain exactly uniform loop dynamics the parameter CN (see Main Synthesiser - Normal Mode) must also change. This can be achieved by either sending a word B for the CN parameter before word A for the frequency or alternatively the extended command A2 can be used to combine both in one long word. This A2 mode is not supported by the ACE9050 as it is not necessary for most cellular terminals.

If Word B is reprogrammed, the new values do not become effective until the next Word A is written. This prevents any spurious conditions during a channel change.

The LG bit in Word D sets whether A or A2 mode is to be used, 0 for A and 1 for A2.

Speed-up drive is active for the duration of the LATCHC pulse that loads the A or A2 word and if it is required the pulse will typically be hundreds of cycles of CL in duration.

In some applications the system performance can be improved by holding LATCHC at HIGH to minimise clock noise on the synthesisers. LATCHC also controls Speed-up mode and so to exit speed-up mode after a channel change the LATCHC must be driven LOW and then a dummy command can be added to get LATCHC back to HIGH. This dummy command should be a non-functional word formed by setting the last four bits to 1111 as in figure 11; the value or the number of the data bits before the four 1's are of no significance so the typical schemes are to send either a standard 24 bit message ending 1111 or a special 4 bit only message of 1111 and in both cases the LATCHC is kept HIGH until the next channel change.

The TEST bits in Word B must be set to 0000 for normal operation and the first two bits in Word B should be set to 00 to be sure of compatibility with future variants.

| BIT STRING | Range of values | FUNCTION                                                                                |

|------------|-----------------|-----------------------------------------------------------------------------------------|

| N1         | 3 - 4095        | Main synthesiser down count; prescaler at lower modulus.                                |

| N2         | 1 - 255         | Main synthesiser up count; prescaler at higher modulus.                                 |

| NF         | 0 - 7           | Main synthesiser fractional increment numerator.                                        |

| TEST       | 0000            | This state must be selected in every Word B for normal operation.                       |

|            |                 | TEST pin will be held LOW to screen adjacent PDA pin.                                   |

|            |                 | Other test modes are for use during chip manufacture only.                              |

| CN         | 0 - 255         | Main charge pump current scaling coefficient.                                           |

| K          | 0 - 15          | Integral charge pump speed-up mode multiplying factor.                                  |

| L          | 0 - 3           | Proportional charge pump speed-up mode exponent, giving x 2, x4, x 8                    |

|            |                 | or x 16 current.                                                                        |

| NA         | 3 - 4095        | Auxiliary synthesiser VCO divider ratio.                                                |

| NR         | 8 - 4095        | Reference divider ratio.                                                                |

| SM         | 0 - 3           | Main synthesiser comparison frequency select.                                           |

| DM         | 0, 1            | Main synthesiser in standby mode if DM set HIGH.                                        |

| SA         | 0 - 3           | Auxiliary synthesiser comparison frequency select.                                      |

| DA         | 0, 1            | Auxiliary synthesiser in standby mode if DA set HIGH.                                   |

| FMOD       | 0, 1            | Fractional-N denominator, $\frac{1}{5}$ 's when at "0" or $\frac{1}{8}$ 's when at "1". |

| LG         | 0, 1            | Control bus mode select - Word A if LOW or Word A2 if HIGH.                             |

# Summary of Synthesiser Programming

#### FUNCTIONAL DESCRIPTION - BLOCKS IN THE RADIO INTERFACE

#### **Power-On Reset Generator**

To ensure a tidy start-up there is an internal power-on detector to initialise various registers.

This initialisation leaves the Radio Interface in Sleep mode with the crystal and 8-064 MHz oscillators running. The 8-064 MHz PLL will be set up for a 15-36 MHz crystal as a default to ensure the microprocessor is not clocked too fast during the start up sequence. Any Normal command can be used to change to active operation.

A software Restart command can be sent to force the Radio Interface to the power-on reset state. This command is:

| DATA1   | DATA2    | DATA3    |

|---------|----------|----------|

| XXXXXXX | 10xxxxxx | xxxxxx11 |

#### **Digital Outputs**

The nine digital outputs, DOUT8 to DOUT0, are used to control the status or function of radio subsections external to the ACE9030 and are controlled by a Normal type command with a logic "1" setting the output to HIGH or ON and a logic "0" giving LOW or OFF.

Outputs DOUT0 and DOUT1 are power switches from  $V_{\text{DDX}}$  to supply Front-End circuits. Both are forced to OFF in Sleep mode.

Outputs DOUT2 to DOUT4 are logic level outputs to control various functions in the cellphone. DOUT2 and DOUT3 are forced to HIGH and DOUT4 is forced to high impedance in Sleep mode.

Outputs DOUT5 to DOUT7 are low current outputs with reduced voltage swing to control power down in the ACE9010 and ACE9020. All three are forced to LOW in Sleep mode.

Output DOUT8 can be driven by the buffered Band-gap based ADC reference voltage and is included for test and setting-up purposes, as well as for driving a temperature sensing thermistor read through one of the ADC channels. DOUT8 is forced to high impedance in Sleep mode.

The control formats are Normal commands:

| DATA1                             | DATA2    | DATA3   |

|-----------------------------------|----------|---------|

| $D_7 D_6 D_5 D_4 D_3 D_2 D_1 D_0$ | 01xxx1xx | xxxxxxx |

where DATA1 bits 7 to 0 control DOUT7 to DOUT0 respectively when enabled by DATA2 bit 2, and:

| DATA1    | DATA2    | DATA3                   |

|----------|----------|-------------------------|

| XXXXXXXX | 01xxxxxx | xx D <sub>5</sub> xxxxx |

where DATA3 bit 5 controls DOUT8 directly.

#### Lock Detect Filter

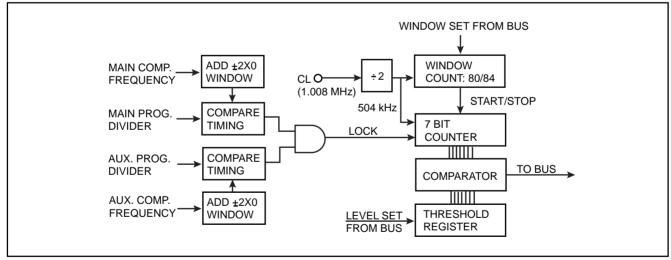

Fig. 12 Lock Detect Block Diagram

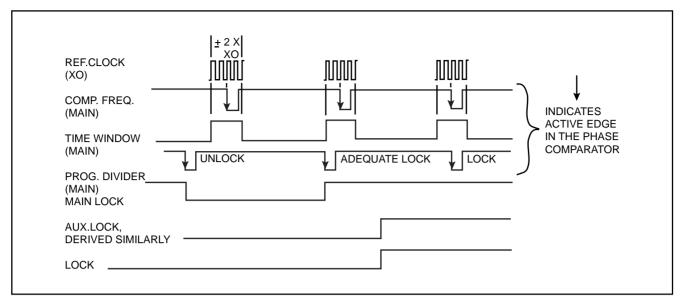

The Lock Detect Filter processes the phase errors in both synthesisers to give a clean signal to put onto the bus as a single bit added to the ADC read response.

In the synthesiser section of the ACE9030 the time differences between the active edges of the outputs of the programmable dividers and of the reference divider are compared with a window of two cycles of the reference clock, XO, from the crystal oscillator. If a loop has a time difference, or phase error, larger than this window then that loop is deemed unlocked and its lock signal is held low for a whole comparison period, giving a Main Lock and an Auxiliary Lock signal. When both synthesisers are active the error signals are combined by an AND function to give the internal signal LOCK. If either synthesiser is powered down its lock is disregarded and if both are powered down the ACE9030 will always give LOCK at LOW, the unlocked state, to be output on the bus. This final signal LOCK is normally HIGH to indicate locked loops but will pulse low for one or more comparison periods when an active synthesiser is unlocked.

Fig. 13 Typical Lock Detect Waveforms

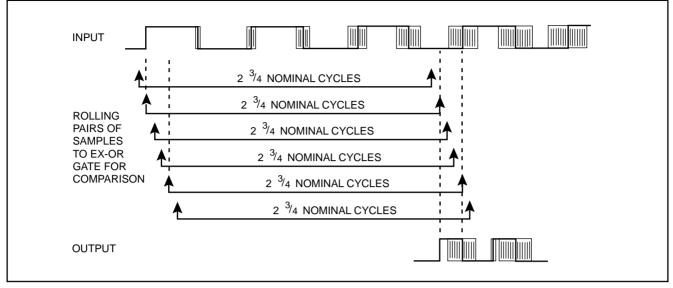

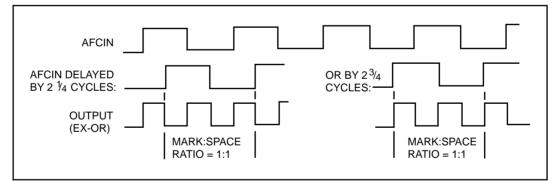

Pulses can occur on the LOCK signal at a rate up to the higher of the Main and Auxiliary comparison frequencies, and typically either 12.5 kHz for ETACS (50 kHz if Fractional-N is used) or 30 kHz for AMPS so some extra filtering is needed to get a clean lock indicator.

LOCK is filtered by first sampling at 504 kHz (the bus clock CL divided by two) and then counting the number of HIGH samples in a pre-determined period. There are two selections available for this counting period, approximately 160  $\mu$ s (2 periods of 12.5 kHz or 8 of 50 kHz) or approximately 167  $\mu$ s (5 periods of 30 kHz) which are set by a second counter, also running at 504 kHz and with a fixed modulus of 80 or 84. LOCK is stable for each comparison period so the counts for each comparison frequency are always in blocks of 40 for 12.5 kHz, 10 for 50 kHz or 16 for 30 kHz.

The value in the LOCK sample counter is compared with a threshold previously set by another bus command, to determine if the loops are locked, the result is then output as the last bit in the pre-amble word in the response to a Normal command, before the ADC levels are given, as described in the section Polling A to D converter.

The filter period is selected by the following Set-up command where DATA1 bit  $D_5$  sets the period to one of the two values to suit whichever cellular system is to be used:

## Polling A To D Converter

A five channel polling Analog to Digital Converter is used to monitor various analog levels, such as Received Signal Strength, Transmitter Power, Temperature and Battery Voltage. The 8 bit ADC has a nominal range of 0.15 V to 3.45 V for codes 00 to FF and is connected to each input channel, ADC1 to ADC5, in turn by the scanning logic. The results are put into individual registers for reading by the microcontroller. The successive approximation technique is used, with the bus clock CL controlling both the timing of the conversion and also the polling around the inputs. The voltage reference for the ADC is shared with the three DAC's and is derived from the bandgap voltage through a trimming multiplier which can be monitored on DOUT8 and is described in the section Band-Gap Reference. Some channels are scanned more frequently than others, with the pattern:

5, 1, 5, 2, 5, 1, 5, 3, 5, 1, 5, 4,

| $xx D_{-} xxxxx$ 10xxxxxx $xx1xxx00$ | DATA1                   | DATA2    | DATA3    |

|--------------------------------------|-------------------------|----------|----------|

|                                      | xx D <sub>5</sub> xxxxx | 10xxxxxx | xx1xxx00 |

DATA1:5 = 0 sets 160  $\mu$ s for ETACS (Window count = 80) and DATA1:5 = 1 sets 167  $\mu$ s for AMPS (Window count = 84).

The threshold is set by a Normal command:

DATA1 bits  $D_7$  to  $D_1$  form a 7 bit binary number in the range

| DATA1                           | DATA2    | DATA3    |

|---------------------------------|----------|----------|

| $D_7 D_6 D_5 D_4 D_3 D_2 D_1 x$ | 01x1xxxx | XXXXXXXX |

0 to 127, which is the threshold value to be loaded. The window period of 80 or 84 clock cycles sets the maximum count value that can be found; the effect of unlock is to reduce the actual count by at least one comparison period's worth of samples 40, 10, or 16 so a suitable threshold can easily be chosen. Assuming that the maximum sensitivity is required the threshold should be set at just above the maximum count (80 or 84) minus the effect of one unlock count (40, 10, or 16), to give suggested thresholds of at least 42 (for 12-5 kHz) or 72 (for 50 kHz) or 70 (for 30 kHz). In each case any convenient number between these suggestions and the maximum count may be used as the selection is not critical.

which repeats continuously. With clock CL at its normal 1008 kHz frequency, the scanning rates are 12.6 kHz for ADC5, 6.3 kHz for ADC1 and 2.1 kHz for ADC2, 3 and 4.

Channels 2 and 3 each have two options, 2A, 2B and 3A, 3B as pins to connect to alternative points to monitor. The selection is by a Set-up command:

| DATA1    | DATA2                                 | DATA3    |

|----------|---------------------------------------|----------|

| XXXXXXXX | 10xxx D <sub>2</sub> D <sub>1</sub> x | xxxxxx00 |

where DATA2 bit  $D_2$  selects ADC3B when HIGH or ADC3A when LOW for measurement by channel 3, and DATA2 bit  $D_1$  selects ADC2B when HIGH or ADC2A when LOW for measurement by channel 2.

The ADC data in the five registers is read in response to a Normal command, with the two results to be output being selected by two bits of DATA3:

| DATA1    | DATA2    | DATA3          |

|----------|----------|----------------|

| XXXXXXXX | 01xxxxxx | $xxxxxXY_1Y_0$ |

where  $Y_1 Y_0$  are decoded to select:

| Y <sub>1</sub> | Y <sub>0</sub> | Data requested |

|----------------|----------------|----------------|

| 0              | 0              | ADC5 & ADC1    |

| 0              | 1              | ADC5 & ADC2A/B |

| 1              | 0              | ADC5 & ADC3A/B |

| 1              | 1              | ADC5 & ADC4    |

The requested data is then clocked out after a fixed delay, with a preamble followed by the two results:

| PREAMBLE                               | RESULT 1 | RESULT 2 |

|----------------------------------------|----------|----------|

| 1010 Y <sub>1</sub> Y <sub>0</sub> 0 L | RRRRRRR  | RRRRRRR  |

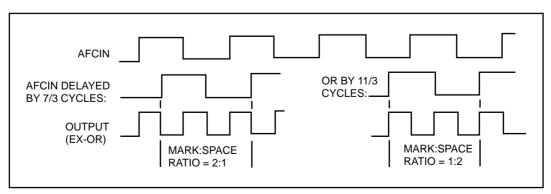

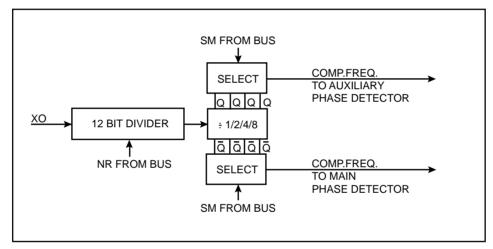

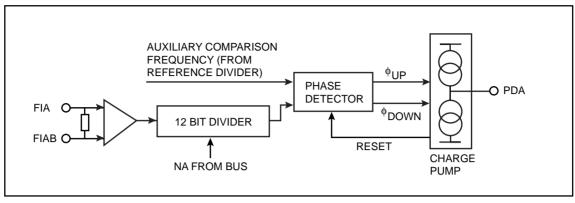

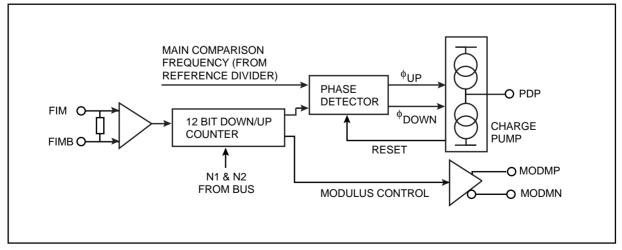

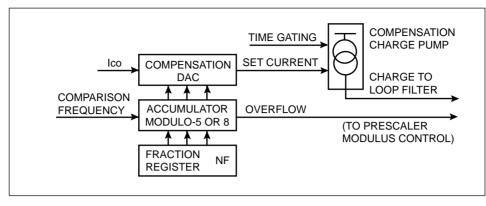

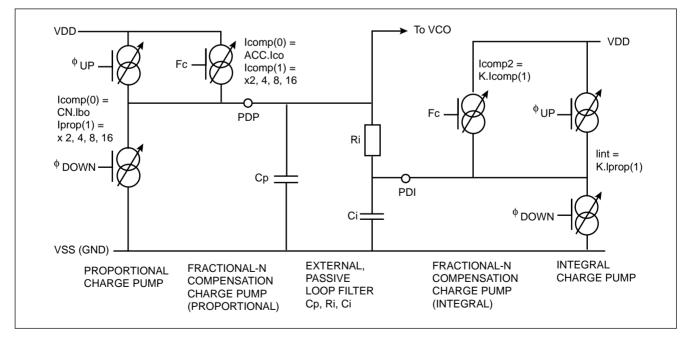

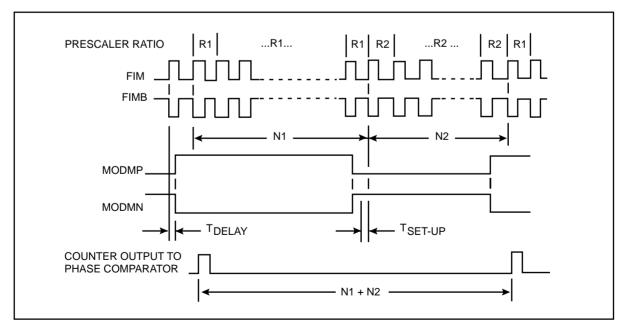

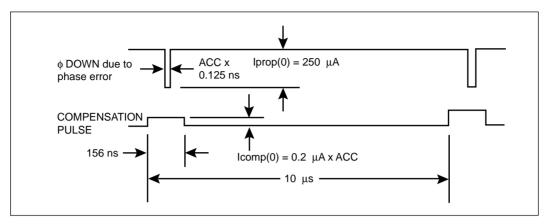

The  $Y_1 Y_0$  code is output to confirm the data selection and is the same as in the Normal command that requested the data, detailed above, L is the Lock Detect status from the Lock Detect Filter, and the two results are in the order ADC5 in RESULT 1 and ADC1, 2, 3, or 4 in RESULT 2.