# 3421 AND 3422

# PRELIMINARY INFORMATION (subject to change without notice) September 6, 2000

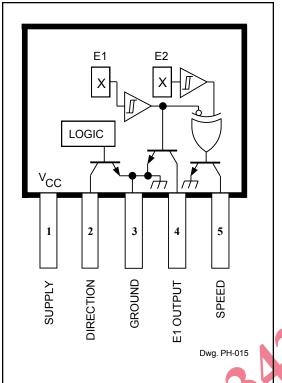

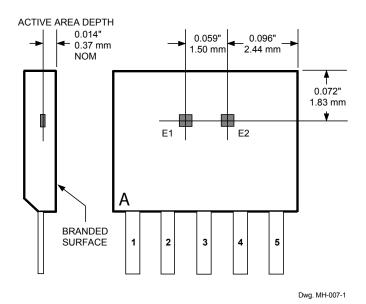

Pinning is shown viewed from branded side.

### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage, $V_{CC}$                    |

|---------------------------------------------|

| Magnetic Flux Density, B Unlimited          |

| Output OFF Voltage, $V_{OUT}$ $V_{CC}$      |

| Output Sink Current, TOUT 30 mA             |

| Package Power Dissipation,                  |

| P <sub>D</sub>                              |

| Operating Temperature Range, T <sub>A</sub> |

| Suffix 'EKA'40 °C to +85 °C                 |

| Suffix 'LKA' 40°C to +150°C                 |

| Storage Temperature Range,                  |

| T <sub>S</sub>                              |

|                                             |

# HALL-EFFECT, DIRECTION-DETECTION SENSOR ICS

The A3421xKA and A3422xKA Hall-effect, direction-detection sensor ICs are a new generation of special-function devices that are capable of sensing the direction of rotation of a ring magnet. These transducers provide separate digital outputs that provide information on magnet rotation speed, direction, and magnet pole count. These devices eliminate the major manufacturing hurdles encountered in fine-pitch direction-detection applications, namely maintaining accurate mechanical location between the two active Hall elements. Here, the two Hall elements are photolithographically aligned to better than  $1 \mu m$ , as contrasted with 100 µm or worse mechanical location tolerance when manufactured discretely. These highly sensitive, temperature-stable, magnetic transducers are ideal for use in digital-encoder systems in the harsh environments of automotive or industrial applications. The A3421xKA is a high-hysteresis device designed for low-resolution pulse counting while the A3422xKA is a high-sensitivity device optimized for use with high-density magnets.

The A3421xKA and A3422xKA monolithic integrated circuits contain two independent Hall-effect latches whose digital outputs are internally coupled to CMOS logic circuitry that decodes signal speed and direction. Extremely low-drift BiCMOS circuitry is used for the amplifiers to ensure symmetry between the two latches so that signal quadrature can be maintained. An on-chip voltage regulator allows the use of these devices from a 4.5 V to 18 V supply. Both devices have standard open-collector outputs; the logic operation of both devices is the same.

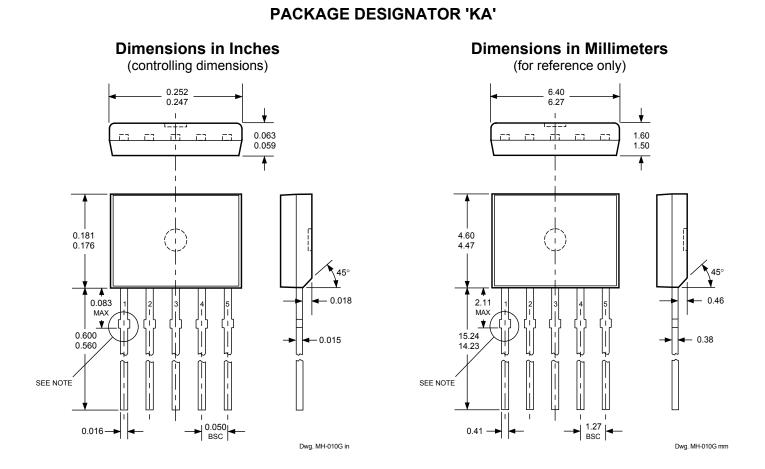

Two operating temperature ranges are provided; suffix 'E-' is for the automotive and industrial temperature range of -40°C to +85°C, suffix 'L-' is for the automotive and military temperature range of -40°C to +150°C. The 5-pin 'KA' SIP package provides a costcompetitive solution to linear magnetic sensing in harsh environments.

# FEATURES

- Internal Direction-Decoding Circuitry

- Two Matched Hall Latches On A Single Substrate

- Superior Temperature Stability

- 4.5 V to 18 V Operation

Electrically Defined Power-On State Under-Voltage Lockout

Always order by complete part number, e.g.,  $\boxed{A3421EKA}$ .

FUNCTIONAL BLOCK DIAGRAM

Dwg. WH-012A

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000 Copyright © 1999 Allegro MicroSystems, Inc.

|                           |                       |                                                                                     | Limits |      |      |       |  |

|---------------------------|-----------------------|-------------------------------------------------------------------------------------|--------|------|------|-------|--|

| Characteristic            | Symbol                | Test Conditions                                                                     | Min.   | Тур. | Max. | Units |  |

| Supply Voltage Range      | V <sub>CC</sub>       | Operating, T <sub>J</sub> < 165°C <sup>1</sup>                                      | 4.5    | _    | 18   | V     |  |

| Output Leakage Current    | I <sub>OFF</sub>      | V <sub>OUT</sub> = V <sub>CC</sub> = 18 V                                           | _      | <1.0 | 10   | μA    |  |

| Output Saturation Voltage | V <sub>OUT(SAT)</sub> | I <sub>OUT</sub> = 20 mA                                                            | _      | 0.21 | 0.50 | V     |  |

| Power-On State            | POS                   | $V_{CC} = 0 \rightarrow 5 V$ ,<br>$B_{RP1} < B < B_{OP1}$ , $B_{RP2} < B < B_{OP2}$ | OFF    | OFF  | OFF  | -     |  |

| Under-Voltage Lockout     | V <sub>CC(UV)</sub>   | $I_{OUT}$ = 20 mA, $V_{CC}$ = 0 $\rightarrow$ 5 V                                   | _      | 3.5  | _    | V     |  |

| Under-Voltage Hysteresis  | V <sub>CC(hys)</sub>  | Lockout (V <sub>CC(UV)</sub> ) - Shutdown                                           | _      | 0.5  | _    | V     |  |

| Power-On Time             | t <sub>po</sub>       | V <sub>CC</sub> > 4.5 V                                                             | _      | _    | 50   | μs    |  |

| Output Rise Time          | t <sub>r</sub>        | $C_L$ = 20 pF, $R_L$ = 820 Ω                                                        | _      | 200  | _    | ns    |  |

| Output Fall Time          | t <sub>f</sub>        | C <sub>L</sub> = 20 pF, R <sub>L</sub> = 820 Ω                                      | _      | 200  | _    | ns    |  |

| Direction Change Delay    | t <sub>d</sub>        | C <sub>L</sub> = 20 pF, R <sub>L</sub> = 820 Ω                                      | 0.5    | 1.0  | 5.0  | μs    |  |

| Supply Current            | I <sub>CC</sub>       | V <sub>CC</sub> = 8 V, All outputs OFF                                              | 5.0    | 9.0  | 18   | mA    |  |

### ELECTRICAL CHARACTERISTICS over operating temperature range.

NOTES: 1. Maximum supply voltage must be adjusted for power dissipation and ambient temperature. 2. Typical Data is at  $V_{CC} = 12$  V and  $T_A = +25$ °C and is for design information only.

|                            |                  |                                     | A3421xKA |      | A3422xKA |      |      |      |       |

|----------------------------|------------------|-------------------------------------|----------|------|----------|------|------|------|-------|

| Characteristic             | Symbol           | Test Conditions                     | Min.     | Тур. | Max.     | Min. | Тур. | Max. | Units |

| Operate Point              | B <sub>OP</sub>  | T <sub>A</sub> = -40°C              | 140      | 185  | 300      | _    | 29   | 85   | G     |

|                            |                  | T <sub>A</sub> = +25°C              | 130      | 160  | 280      | _    | 29   | 75   | G     |

|                            |                  | T <sub>A</sub> = Maximum            | 120      | _    | 260      | _    | _    | 75   | G     |

| Release Point <sup>3</sup> | B <sub>RP</sub>  | T <sub>A</sub> = -40°C              | -300     | -190 | -140     | -85  | -19  |      | G     |

|                            |                  | T <sub>A</sub> = +25°C              | -280     | -175 | -130     | -75  | -18  | _    | G     |

|                            |                  | T <sub>A</sub> = Maximum            | -260     | —    | -120     | -75  | -16  | —    | G     |

| Hysteresis                 | B <sub>hys</sub> | T <sub>A</sub> = -40°C              | 280      | 375  | —        | 10   | 48   |      | G     |

|                            |                  | T <sub>A</sub> = +25°C              | 260      | 335  | —        | 10   | 46   | _    | G     |

|                            |                  | T <sub>A</sub> = Maximum            | 240      | _    |          | 10   |      |      | G     |

| Operate Differential       |                  | B <sub>OP1</sub> - B <sub>OP2</sub> |          |      | ±80      | _    |      | ±60  | G     |

| Release Differential       |                  | B <sub>RP1</sub> - B <sub>RP2</sub> |          | _    | ±80      | _    | _    | ±60  | G     |

### MAGNETIC CHARACTERISTICS over operating voltage range.

NOTES:1. Magnetic flux density is measured at most sensitive area of device,

- nominally located 0.014" (0.37 mm) below the branded face of the package.

- 2. Typical Data is at  $V_{CC}$  = 12 V and  $T_A$  = +25°C and is for design information only.

- 3. As used here, negative flux densities are defined as less than zero (algebraic convention).

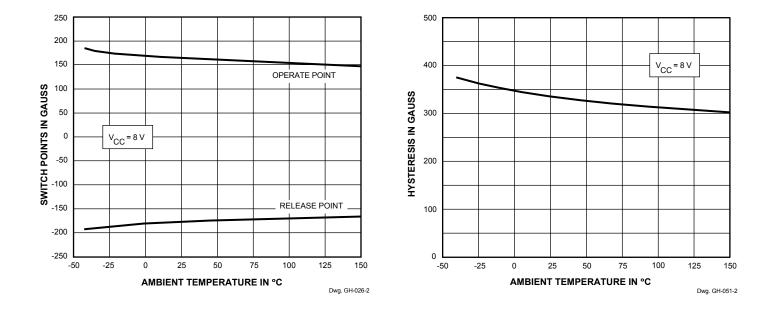

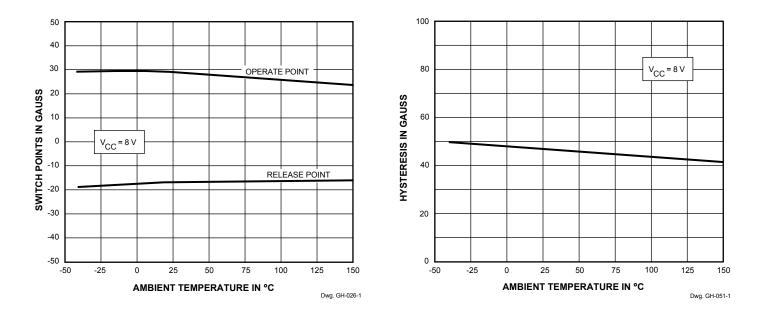

### **TYPICAL A3421xKA CHARACTERISTICS**

**TYPICAL A3422xKA CHARACTERISTICS**

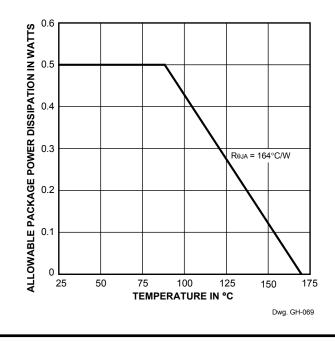

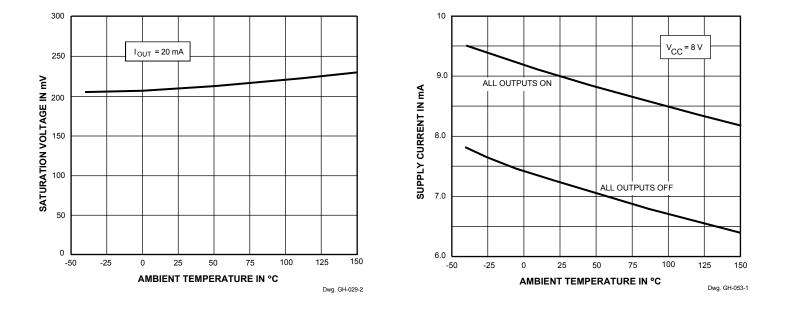

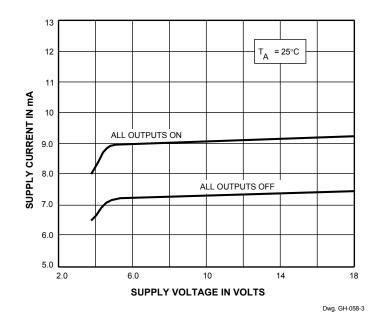

### **TYPICAL ELECTRICAL CHARACTERISTICS**

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000

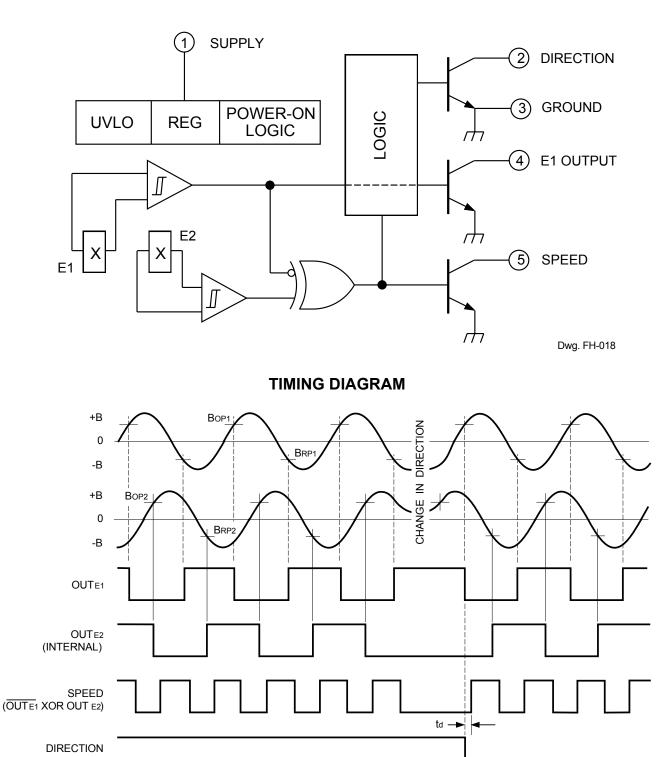

### FUNCTIONAL DESCRIPTION

The integrated circuit contains an internal voltage regulator that powers the Hall elements and both the analog and digital circuitry. This regulator allows operation over a wide supply voltage range and provides some immunity to supply noise. The device also contains CMOS logic circuitry that decodes the direction of rotation of the ring magnet.

Quadrature/Direction Detection. Internal logic circuitry provides outputs representing speed and direction of the magnetic field across the face of the package. For the direction signal to be appropriately updated, a quadrature relationship must be maintained between the ring magnet pole width\*, the element-to-element spacing, and, to a lesser extent, the magnetic switch points. For optimal design, the device should be actuated with a ring magnet pole width\* two times the sensor-to-sensor spacing. This will produce a sinusoidal magnetic field whose period (denoted as T) is then four times the element-to-element spacing. A quadrature relationship can also be maintained for a ring magnet that has a period that satisfies the relationship nT/4 = 1.5 mm, where n is any odd integer. Therefore, ring magnets with pole-pair spacings equal to 6 mm (n = 1), 2 mm (n = 3), 1.2 mm (n = 5), etc. are permitted.

The response of the device to the magnetic field produced by a rotating ring magnet is shown on page 2. Note the phase shift between the two elements. **Outputs.** The device provides three saturated outputs: DIRECTION, E1 OUTPUT, and SPEED. DIRECTION provides the direction output of the device and is defined as OFF (high) for the direction E1 to E2 and ON (low) for the direction E2 to E1. SPEED provides an XOR'd output of the two elements. Because of internal delays, DIREC-TION will always be updated before SPEED and is updated at every transition of E1 OUTPUT and E2 OUT-PUT (internal) allowing the use of up-down counters without the loss of pulses.

**Power-On State.** At power on, the logic circutry is reset to provide an OFF (high) at DIRECTION and an OFF (high) for E1 and E2 (internal) for magnetic fields less than  $B_{OP}$ . This eliminates ambiguity when the device is powered up and either element detects a field between  $B_{P}$  and  $B_{RP}$ . If either element is subjected to a field greater than  $B_{OP}$ , the internal logic will set accordingly.

\*"Pole" refers to a single pole (North or South) unless stated as "pole pair" (North <u>and</u> South).

### **APPLICATIONS INFORMATION**

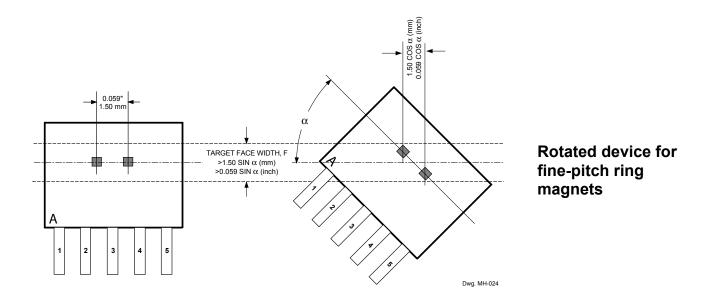

### **Operation with Fine-Pitch Ring Magnets.** For

targets with a circular pitch of less than 4mm, a performance improvement can be observed by rotating the front face of the device (see below). This device rotation decreases the effective element-to-element spacing, provided that the Hall elements are not rotated beyond the width of the target. **Applications.** It is strongly recommended that an external 0.01  $\mu$ F bypass capacitor be connected (in close proximity to the Hall elements) between the supply and ground of the device to reduce both external noise and noise generated by the internal logic.

The simplest form of magnet that will operate these devices is a ring magnet. Other methods of operation, such as linear magnets, are possible. Extensive applications information on magnets and Hall-effect devices is also available in the "Hsall-Effect IC Applications Guide" which can be found in the latest issue of the *Allegro MicroSystems Electronic Data Book,* AMS-702 or *Application Note* 27701, or at

www.allegromicro.com

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000

### **CRITERIA FOR DEVICE QUALIFICATION**

All Allegro devices are subjected to stringent qualification requirements prior to being released to production. To become qualified, except for the destructive ESD tests, no failures are permitted.

| Qualification Test                      | Test Method and<br>Test Conditions                             | Test Length         | Samples<br>Per Lot | Comments                            |

|-----------------------------------------|----------------------------------------------------------------|---------------------|--------------------|-------------------------------------|

| Temperature Humidity<br>Bias Life       | JESD22-A101,<br>T <sub>A</sub> = 85°C, RH = 85%                | 1000 hrs            | 77                 | Device biased for minimum power     |

| Bias Life                               | JESD22-A108,<br>T <sub>A</sub> = 150°C, T <sub>J</sub> = 165°C | 1000 hrs            | 77                 |                                     |

| (Surge Operating Life)                  | JESD22-A108,<br>T <sub>A</sub> = 175°C, T <sub>J</sub> = 190°C | 1000 hrs            | 77                 |                                     |

| Autoclave, Unbiased                     | JESD22-A102,<br>T <sub>A</sub> = 121°C, 15 psig                | 96 hrs              | 77                 |                                     |

| High-Temperature<br>(Bake) Storage Life | JESD22-A103,<br>T <sub>A</sub> = 170°C                         | 1000 hrs            | 77                 |                                     |

| Temperature Cycle                       | JESD22-A104                                                    | 1000 cycles         | 77                 | -55°C to +150°C                     |

| ESD,<br>Human Body Model                | CDF-AEC-Q100-002                                               | Pre/Post<br>Reading | 3 per<br>test      | Test to failure<br>All leads > 8 kV |

### **ELEMENT LOCATIONS**

(±0.005" [0.13 mm] die placement)

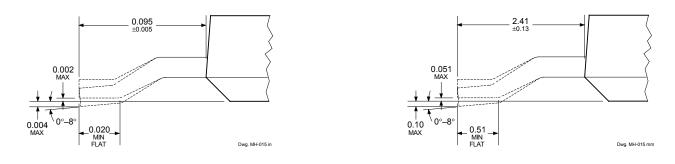

### SURFACE-MOUNT LEAD FORM (Suffix '-TL')

NOTES: 1. Tolerances on package height and width represent allowable mold offsets. Dimensions given are measured at the widest point (parting line).

- 2. Exact body and lead configuration at vendor's option within limits shown.

- 3. Height does not include mold gate flash.

- 4. Recommended minimum PWB hole diameter to clear transition area is 0.035" (0.89 mm).

- 5. Where no tolerance is specified, dimension is nominal.

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the design of its products.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.