### ADCOS-1403 ADCOS-1403 In A DIT SIGNAL PROCESSOR IN A GING SIGNAL PROCESSOR

#### **FEATURES**

- 14-bit resolution

- 3MPPS throughput rate (14-bits)

- Functionally complete

- Very low noise

- Excellent Signal-to-Noise ratio

- Edge triggered

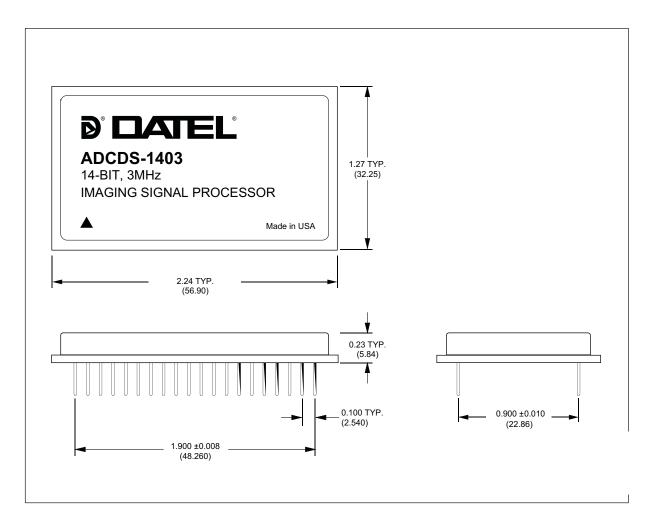

- Small, 40-pin, TDIP package

- Low power, 500mW typical

- Low cost

- Programmable Analog Bandwidth

#### **PRODUCT OVERVIEW**

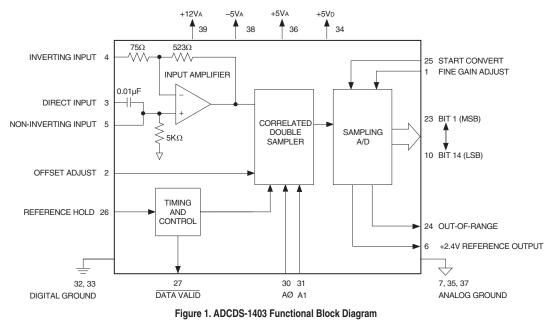

The ADCDS-1403 is an application-specific video signal processor designed for electronicimaging applications that employ CCD's (charge coupled devices) as their photodetector. The ADCDS-1403 incorporates a "user configurable" input amplifier, a CDS (correlated double sampler) and a sampling A/D converter in a single package, providing the user with a complete, high performance, low-cost, low-power, integrated solution.

The key to the ADCDS-1403's performance is a unique, high-speed, high-accuracy CDS circuit, which eliminates the effects of residual charge, charge injection and "kT/C" noise on the CCD's output floating capacitor, producing a "valid video" output signal. The ADCDS-1403 digitizes this resultant "valid video" signal using a high-speed, low-noise sampling A/D converter.

14-Bit, 3 Megapixels/Second Imaging Signal Processor

The ADCDS-1403 requires only the rising edge of start convert pulse to initiate its conversion process. Additional features of the ADCDS-1403 include gain adjust, offset adjust, precision +2.4V reference, and a programmable analog bandwidth function.

|     | INPUT/OUTPU         | T CONI | NECTIONS       |

|-----|---------------------|--------|----------------|

| Pin | Function            | Pin    | Function       |

| 1   | FINE GAIN ADJUST    | 40     | NO CONNECT     |

| 2   | OFFSET ADJUST       | 39     | +12V           |

| 3   | DIRECT INPUT        | 38     | -5VA           |

| 4   | INVERTING INPUT     | 37     | ANALOG GROUND  |

| 5   | NON-INVERTING INPUT | 36     | +5VA           |

| 6   | +2.4V REF. OUTPUT   | 35     | ANALOG GROUND  |

| 7   | ANALOG GROUND       | 34     | +5VD           |

| 8   | NO CONNECT          | 33     | DIGITAL GROUND |

| 9   | NO CONNECT          | 32     | DIGITAL GROUND |

| 10  | BIT 14 (LSB)        | 31     | A1             |

| 11  | BIT 13              | 30     | AØ             |

| 12  | BIT 12              | 29     | NO CONNECT     |

| 13  | BIT 11              | 28     | NO CONNECT     |

| 14  | BIT 10              | 27     | DATA VALID     |

| 15  | BIT 9               | 26     | REFERENCE HOLD |

| 16  | BIT 8               | 25     | START CONVERT  |

| 17  | BIT 7               | 24     | OUT-OF-RANGE   |

| 18  | BIT 6               | 23     | BIT 1 (MSB)    |

| 19  | BIT 5               | 22     | BIT 2          |

| 20  | BIT 4               | 21     | BIT 3          |

www.murata-ps.com

Technical enquiries email: data.acquisition@murata-ps.com, tel: +1 508 339 3000

# Murata Ps Murata Power Solutions ADCDS-1403 14-Bit, 3 Megapixels/Second Imaging Signal Processor

# **ADCDS-1403**

| ABSOLUTE MAXIMUM RATINGS           |      |      |          |       |

|------------------------------------|------|------|----------|-------|

| PARAMETERS                         | MIN. | TYP. | MAX.     | UNITS |

| +12V Supply (Pin 32)               | 0    | _    | +14      | Volts |

| –5V Supply (Pin 38)                | -6.5 | _    | +0.3     | Volts |

| +5V Supply (Pin 34, 36)            | -0.3 | _    | +6.5     | Volts |

| Digital Input (Pin 25, 26, 30, 31) | -0.3 | _    | Vdd+0.3V | Volts |

| Analog Input (Pin 3,4,5)           | -6   | —    | +6       | Volts |

| Lead Temperature (10 seconds)      | —    | —    | 300      | °C    |

#### **Functional Specifications**

The following specifications apply over the operating temperature range, under the following conditions: Vcc=+12V, +Vdd=+5V, Vee=-5V, fin=98KHz, sample rate=3MHz.

| ANALOG INPUT                                                                                                  | MIN.                            | TYP.                    | MAX.                    | UNITS                            |

|---------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------|-------------------------|----------------------------------|

| Input Voltage Range<br>(externally configurable)<br>Input Resistance<br>Input Capacitance                     | 0.350                           | 2.8<br>5000<br>10       |                         | Volts p-p<br>Ohm<br>pF           |

| DIGITAL INPUTS                                                                                                |                                 |                         |                         | -                                |

| Logic Level<br>Logic 1<br>Logic 0<br>Logic Loading<br>Logic 1<br>Logic 0                                      | +3.5<br>—                       |                         | <br>+.80<br>+10<br>-10  | Volts<br>Volts<br>uA<br>uA       |

| DIGITAL OUTPUTS                                                                                               |                                 |                         |                         |                                  |

| Logic Levels<br>Logic 1 (IOH = .5ma)<br>Logic 1 (IOH = 50µa)<br>Logic 0 (IOL = 1.6ma)<br>Logic 0 (IOL = 50µa) | +2.4<br>+4.5<br>                |                         | <br>+0.4<br>+0.1        | Volts<br>Volts<br>Volts<br>Volts |

| Internal Reference<br>Voltage<br>(Fine gain adjust pin (1) grounded)<br>+25°C<br>0 to 70°C<br>-55 to +125°C   | 2.35<br>2.35<br>2.35            | 2.4<br>2.4<br>2.4       | 2.45<br>2.45<br>2.45    | Volts<br>Volts<br>Volts          |

| External Current                                                                                              |                                 | 1.0                     |                         | mA                               |

| STATIC<br>Differential Nonlinearity<br>(Histogram, 98kHz) +25°C<br>0 to 70°C<br>-55 to +125°C                 | -0.90<br>-0.90<br>-0.90<br>-1.0 | ±0.5<br>±0.5<br>±0.6    | +.90<br>+.90<br>+1.0    | LSB<br>LSB<br>LSB                |

| Integral Nonlinearity<br>+25°C<br>0 to 70°C<br>-55 to +125°C                                                  |                                 | ±2.5<br>±2.5<br>±2.5    |                         | LSB<br>LSB<br>LSB                |

| Guaranteed No Missing Codes<br>0 to 70°C<br>–55 to +125°C                                                     | 14<br>14                        |                         | _                       | LSB<br>LSB                       |

| DC Noise<br>+25°C<br>0 to 70°C<br>-55 to +125°C                                                               | <br><br>                        | 1.0<br>1.0<br>1.25      | 1.6<br>2.0<br>2.5       | LSB<br>LSB<br>LSB                |

| Offset Error<br>+25°C<br>0 to 70°C<br>-55 to +125°C                                                           |                                 | ±0.6<br>±0.6<br>±0.6    | ±1.25<br>±1.25<br>±1.45 | %FSR<br>%FSR<br>%FSR             |

| Gain Error<br>+25°C<br>0 to 70°C<br>-55 to +125°C                                                             |                                 | ±1.00<br>±1.35<br>±1.35 | ±2.8<br>±2.8<br>±2.8    | %FSR<br>%FSR<br>%FSR             |

| DYNAMIC PERFORMANCE                                                                                                                                                                                                                                                                                                                                                                                            | MIN.                             | TYP.                                   | MAX.                    | UNITS                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------|-------------------------|----------------------------------|

| Reference Hold                                                                                                                                                                                                                                                                                                                                                                                                 |                                  |                                        |                         |                                  |

| Aquisition Time<br>Droop                                                                                                                                                                                                                                                                                                                                                                                       | 100                              | _                                      | —                       | ns                               |

| @ +25°C                                                                                                                                                                                                                                                                                                                                                                                                        | _                                | 25                                     | _                       | mV/us                            |

| @ -55 to +125°C                                                                                                                                                                                                                                                                                                                                                                                                | -                                | 100                                    | _                       | mV/us                            |

| Peak Harmonic (SFDR)<br>(CDD-IN, input on pin (3)<br>Input @ 98kHz)<br>@ +25 °C<br>@ 0 to +70°C<br>@ -55 to +125°C                                                                                                                                                                                                                                                                                             |                                  | 76<br>76<br>74                         |                         | dB<br>dB<br>dB                   |

| Peak Harmonic (SFDR)                                                                                                                                                                                                                                                                                                                                                                                           |                                  |                                        |                         |                                  |

| (Input on pin (5)<br>Input @ 98kHz)<br>@ +25 °C<br>@ 0 to +70°C<br>@ -55 to +125°C                                                                                                                                                                                                                                                                                                                             | <br><br>_                        | 76<br>76<br>74                         | <br><br>_               | dB<br>dB<br>dB                   |

| Total Harmonic Distortion<br>(CDD-IN, input on pin (3)                                                                                                                                                                                                                                                                                                                                                         |                                  |                                        |                         |                                  |

| Input @ 98kHz)<br>@ +25 °C<br>@ 0 to +70°C<br>@ -55 to +125°C<br>(Input on pin (5)                                                                                                                                                                                                                                                                                                                             | <br><br>                         | 75<br>75<br>74                         | <br><br>                | dB<br>dB<br>dB                   |

| Input @ 98kHz)<br>@ +25 °C                                                                                                                                                                                                                                                                                                                                                                                     | _                                | -76                                    | _                       | dB                               |

| @ 0 to +70°C<br>@ -55 to +125°C                                                                                                                                                                                                                                                                                                                                                                                |                                  | -76<br>-74                             | _                       | dB<br>dB                         |

| Signal-to-Noise Ratio<br>Without Distortion<br>(CDD-IN, input on pin (3)<br>Input @ 98kHz)<br>@ $+25 \circ$ C<br>@ 0 to $+70^{\circ}$ C<br>@ $-55$ to $+125^{\circ}$ C<br>(Input on pin (5)<br>Input @ 98kHz)<br>@ $+25 \circ$ C<br>@ 0 to $+70^{\circ}$ C<br>@ 0 to $+70^{\circ}$ C<br>@ $-55$ to $+125^{\circ}$ C<br>Signal-to-Noise Ratio<br>With Distortion<br>(CDD-IN, input on pin (3)<br>Input @ 98kHz) | 73<br>73<br>70<br>73<br>73<br>70 | 75<br>75<br>73<br>75<br>75<br>75<br>73 | <br>                    | dB<br>dB<br>dB<br>dB<br>dB<br>dB |

| @ +25 °C<br>@ 0 to +70°C<br>@ -55 to +125°C<br>(Input on pin (5)                                                                                                                                                                                                                                                                                                                                               |                                  | 71<br>71<br>70                         |                         | dB<br>dB<br>dB                   |

| Input @ 98kHz)<br>@ +25 °C<br>@ 0 to +70°C<br>@ -55 to +125°C                                                                                                                                                                                                                                                                                                                                                  |                                  | 71<br>71<br>70                         |                         | dB<br>dB<br>dB                   |

| SIGNAL TIMING                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |                                        |                         |                                  |

| Conversion Rate<br>-55 to +125°C<br>Conversion Time<br>Start Convert Pulse Width                                                                                                                                                                                                                                                                                                                               | 3<br><br>20                      | —<br>200<br>150                        |                         | MHz<br>nsec<br>nsec              |

|                                                                                                                                                                                                                                                                                                                                                                                                                | R REQUIREM                       | ENTS                                   |                         |                                  |

| Power Supply Range<br>+12V Supply<br>+5V Supply<br>–5V Supply                                                                                                                                                                                                                                                                                                                                                  | +11.4<br>+4.75<br>-4.75          | +12.0<br>+5.0<br>-5.0                  | +12.6<br>+5.25<br>-5.25 | Volts<br>Volts<br>Volts          |

Technical enquiries email: sales@murata-ps.com, tel: +1 508 339 3000

#### <u>muRata</u> Ps Murata Power Solutions 14-Bit, 3 Megapixels/Second Imaging Signal Processor

#### POWER REQUIREMENTS MIN. MAX. TYP UNITS **Power Supply Current** +12V Supply +13 +16 mΑ Power Supply Current +5V Supply +40+46 mΑ -27 -35 -5V Supply mΑ Power Dissipation 0.50 0.60 Watts Power Supply Rejection (5%) @ +25°C ±0.02 ±0.03 %FSR/%V ENVIRONMENTAL **Operating Temperature Range** 0 °C ADCDS-1403 +70ADCDS-1403EX -55 +125 °C °C Storage Temperature -65 +150 40-pin, TDIP Package Type Weight 16.10 grams

#### **TECHNICAL NOTES**

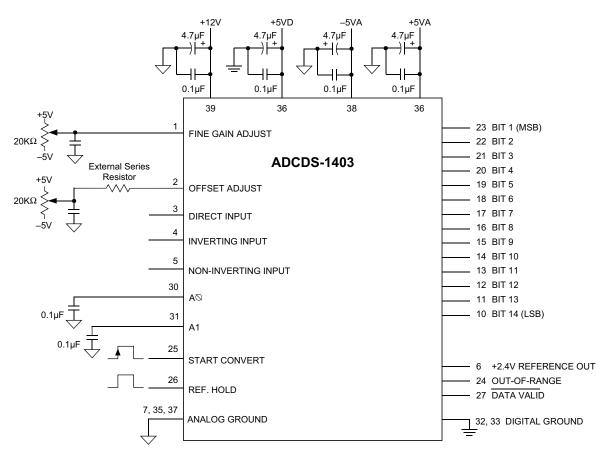

- 1. Obtaining fully specified performance from the ADCDS-1403 requires careful attention to pc-card layout and power supply decoupling. The device's analog and digital grounds are connected to each other internally. Depending on the level of digital switching noise in the overall CCD system, the performance of the ADCDS-1403 may be improved by connecting all ground pins (7,32,33,35, 37) to a large analog ground plane beneath the package. The use of a single +5V analog supply for both the  $+5V_{A}$  (pin 36) and  $+5V_{D}$  (pin 34) may also be beneficial.

- 2. Bypass all power supplies to ground with a 4.7 uf tantalum capacitor in parallel with a 0.1µf ceramic capacitor. Locate the capacitors as close to the package as possible.

- 3. If using the suggested offset and gain adjust circuits (Figure 3 & 5), place them as close to the ADCDS-1403's package as possible.

- 4. A0 and A1 (pins 30, 31) should be bypassed with 0.1 uf capacitors to ground to reduce susceptibility to noise.

#### ADCDS-1403 Modes of Operation

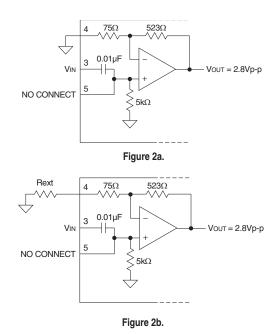

The input amplifier stage of the ADCDS-1403 provides the designer with a tremendous amount of flexibility. The architecture of the ADCDS-1403 allows its input-amplifier to be configured in any of the following configurations:

- Direct Mode (AC coupled)

- Non-Inverting Mode

- Inverting Mode

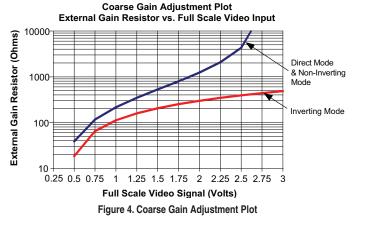

When applying inputs which are less than 2.8Vp-p, a coarse gain adjustment (applying an external resistor to pin 4) must be performed to ensure that the full scale video input signal (saturated signal) produces a 2.8Vp-p signal at the input-amplifier's output (Vout).

In all three modes of operation, the video portion of the signal at the CDS input (i.e. input-amplifier's Vout) must be more negative than its associated reference level and Vout should

not exceed ±2.8V DC.

The ADCDS-1403 achieves it specified accuracies without the need for external calibration. If required, the device's small initial offset and gain errors can be reduced to zero using the FINE GAIN ADJUST (pin1) and OFFSET ADJUST (pin 2) features.

#### **Direct Mode (AC Coupled)**

This is the most common input configuration as it allows the ADCDS-1403 to interface directly to the output of the CCD with a minimum amount of analog "front-end" circuitry. This mode of operation is used with fullscale video input signals from 0.350Vp-p to 2.8Vp-p.

Figure 2a. describes the typical configuration for applications using a video input signal with a maximum amplitude of 0.350Vp-p. The coarse gain of the input amplifier is determined from the following equation: VOUT = 2.8Vp-p = VIN\*(1+(523/75)), with all internal resistors having a 1% tolerance. Additional fine gain adjustment can be accomplished using the Fine Gain Adjust (pin 1 see Figure 5).

Figure 2b. describes the typical configuration for applications using a video input signal with an amplitude greater than 0.350Vp-p and less than 2.8Vp-p. Using a single external series resistor (see Figure 4.), the coarse gain of the ADCDS-1403 can be set, with additional fine gain adjustments being made using the Fine Gain Adjust function (pin 1 see Figure 5). The coarse gain of the input amplifier can be determined from the following equation:

VOUT = 2.8Vp-p = V<sub>IN</sub>\*(1+(523/(75+Rext))), with all internal resistors having a 1% tolerance.

www.murata-ps.com

### **ADCDS-1403**

# **ADCDS-1403**

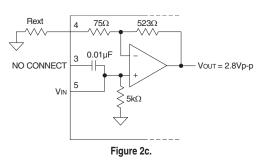

#### **Non-Inverting Mode**

The non-inverting mode of the ADCDS-1403 allows the designer to either attenuate or add non-inverting gain to the video input signal. This configuration also allows bypassing the ADCDS-1403's internal coupling capacitor, allowing the user to provide an external capacitor of appropriate value.

Figure 2c. describes the typical configuration for applications using video input signals with amplitudes greater than

0.350Vp-p and less than 2.8Vp-p (with common mode limit of  $\pm 2.5V$  DC). Using a single external series resistor (see Figure 4.), the coarse gain of the ADCDS-1403 can be set with additional fine gain adjustments being made using the Fine Gain Adjust function (pin 1 see Figure 5). The coarse gain of the circuit can be determined from the following equation:

$V_{OUT} = 2.8Vp-p = V_{IN}*(1+(523/(75+Rext))))$ , with all internal resistors having a 1% tolerance.

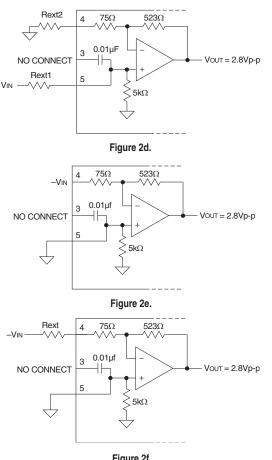

Figure 2d. describes the typical configuration for applications using a video input signal whose amplitude is greater than 2.8Vp-p. Using a single external series resistor (Rext 1) in conjunction with the internal 5K (1%) resistor to ground, an attenuation of the input signal can be achieved. Additional fine gain adjustments being made using the Fine Gain Adjust function (pin 1). The coarse gain of this circuit can be determined from the following equation:

$V_{OUT} = 2.8Vp-p = [V_{IN}*(5000/(Rext1+5000))]*$ [1+(523/(75+Rext2))], with all internal resistors having a 1% tolerance.

#### 14-Bit, 3 Megapixels/Second Imaging Signal Processor

#### **Inverting Mode**

The inverting mode of operation can be used in applications where the analog input to the ADCDS-1403 has a video input signal whose amplitude is more positive than its associated reference level. The ADCDS-1403's correlated double sampler (i.e. input amplifier's Vout) requires that the video signal's amplitude be more negative than its reference level at all times (see timing diagram for details). Using the ADCDS-1403 in the inverting mode allows the designer to perform an additional signal inversion to correct for any analog "front end" pre-processing that may have occurred prior to the ADCDS-1403.

Figure 2e. describes the typical configuration for applications using a video input signal with a maximum amplitude of 0.350Vp-p. Additional fine gain adjustments can be made using the Fine Gain Adjust function (pin 1). The coarse gain of this circuit can be determined from the following equation:

$V_{0UT} = 2.8Vp-p = -V_{IN}^{*}(523/75)$ , with all internal resistors having a 1% tolerance.

Figure 2f. describes the typical configuration used in applications needing to invert video input signals whose amplitude is greater than 0.350Vp-p. Using a single external series resistor (see Figure 4.), the initial gain of the ADCDS-1403 can be set, with additional fine gain adjustments being made using the Fine Gain Adjust function (pin 1). The coarse gain of this circuit can be determined from the following equation:

$V_{0UT} = 2.8Vp-p = -V_{IN}*(523/75+Rext)$ , with all internal resistors having a 1% tolerance.

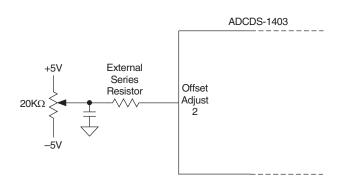

Figure 3. Offset Adjustment Circuit

Figure 2f.

DATE

www.murata-ps.com

Technical enquiries email: sales@murata-ps.com, tel: +1 508 339 3000

# **ADCDS-1403**

#### **Offset Adjustment**

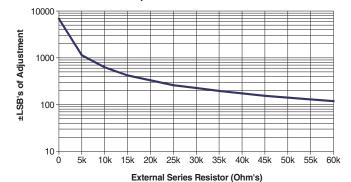

Manual offset adjustment for the ADCDS-1403 can be accomplished using the adjustment circuit shown in Figure 3. A software controlled D/A converter can be substituted for the  $20K\Omega$  potentiometer. The offset adjustment feature allows the user to adjust the Offset/Dark Current level of the ADCDS-1403 until the output bits are 00 0000 0000 0000 and the LSB flickers between 0 and 1. Offset adjust should be performed before gain adjust to avoid interaction. The ADCDS-1403's offset adjustment is dependent on the value of the external series resistor used in the offset adjust circuit (Figure 3). The Offset Adjustment graph (Figure 6) illustrates the typical relationship between the external series resistor value and its offset adjustment capability utilizing  $\pm$ 5V supplies.

#### **Offset Adjustment Sensitivity**

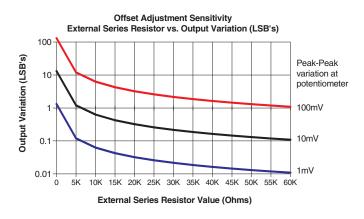

It should be noted that with increasing amounts of offset adjustment (smaller values of external series resistors), the ADCDS-1403 becomes more susceptible to power supply noise or voltage variations seen at the wiper of the offset potentiometer.

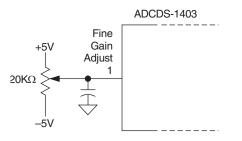

Figure 5. Fine Gain Adjustment Circuit

Offset Adjustment vs. External Series Resistor

#### 14-Bit, 3 Megapixels/Second Imaging Signal Processor

#### For Example:

#### External 50KΩ resistor:

- 1. 10mV of noise or voltage variation at the potentiometer will produce 0.25LSB's of output variation.

- 100mV of noise or voltage variation at the potentiometer will produce 2.5LSB's of output variation.

The Offset Adjustment Sensitivity graph (Figure 7) illustrates the offset adjustment sensitivity over a wide range of external resistor and noise values. If a large offset voltage is required, it is recommended that a very low noise external reference be used in the offset adjust circuit in place of power supplies. The ADCDS-1403's +2.4V reference output could be configured to provide the reference voltage for this type of application.

#### Fine Gain Adjustment

Fine gain adjustment (pin 1) is provided to compensate for the tolerance of the external coarse gain resistor (Rext) and/or the unavailability of exact coarse gain resistor (Rext) values. Note, the fine gain adjustment will not change the <u>expected</u> input amplifier's full scale Vout (2.8Vp-p.) Instead, the gain of the ADCDS-1403's internal A/D is adjusted allowing the <u>actual</u> input amplifier's full scale Vout to produce an output code of all ones (11 1111 1111 1111).

Fine gain adjustment for the ADCDS-1403 is accomplished using the adjustment circuit shown below (Figure 5). A software controlled D/A converter can be substituted for the  $20K\Omega$  potentiometer. The fine gain adjust circuit ensures that the video input signal (saturated signal) will be properly scaled to obtain the desired Full Scale digital output of 11 1111 1111 1111, with the LSB flickering between 0 and 1. Fine gain adjust should be performed following the offset adjust to avoid interaction. The fine gain adjust provides ±256 codes of adjust when ±5V supplies are used for the Fine Gain Adjust Circuit.

Figure 7. Offset Adjustment Sensitivity

Figure 6. Offset Adjustment vs. External Series Resistor

# **ADCDS-1403**

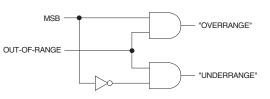

#### **Out-of-Range Indicator**

The ADCDS-1403 provides a digital Out-of-Range output signal (pin 24) for situations when the video input signal (saturated signal) is beyond the input range of the internal A/D converter. The digital output bits and the Out-of-Range signal correspond to a particular sampled video input voltage, with both of these signals having a common pipeline delay.

Using the circuit described in Figure 8., both overrange and underrange conditions can be detected (see Table 1). When combined with a D/A converter, digital detection and orrection can be performed for both the gain and offset errors.

Figure 8. Overrange/ Underrange Circuit

| out of<br>Range | MSB | over<br>Range | UNDER RANGE | INPUT SIGNAL |

|-----------------|-----|---------------|-------------|--------------|

| 0               | 0   | 0             | 0           | In Range     |

| 0               | 1   | 0             | 0           | In Range     |

| 1               | 0   | 0             | 1           | Underrrange  |

| 1               | 1   | 1             | 0           | Overrange    |

#### 14-Bit, 3 Megapixels/Second Imaging Signal Processor

#### Output Coding

The ADCDS-1403's output coding is Straight Binary as indicated in Table 2. The table shows the relationship between the output data coding and the difference between the reference signal voltage and its corresponding video signal voltage. (These voltages are referred to the output of the ADCDS-1403's input amplifier's Vour).

#### **Programmable Analog Bandwidth Function**

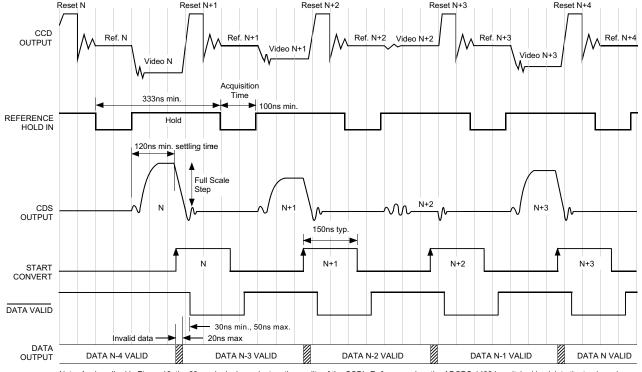

When interfacing to CCD arrays with very high-speed "read-out" rates, the ADCDS-1403's input stage must have sufficient analog bandwidth to accurately reproduce the output signals of the CCD array. The amount of analog bandwidth determines how quickly and accurately the "Reference Hold" and the "CDS output" signals will settle. If only a single analog bandwidth was offered, the ADCDS-1403's bandwidth would be set to acquire and digitize CCD output signals to 14-bit accuracy, at maximum conversion rate of 3MHz (333ns see Figure 11. for details). Applications not requiring the maximum conversion rate would be forced to use the full analog bandwidth at the possible expense of noise performance.

The ADCDS-1403 avoids this situation by offering a fully programmable analog bandwidth function. The ADCDS-1403 allows the user to "bandwidth limit" the input stage in order to realize the highest level of noise performance for the application being considered. Table 3. describes how to select the appropriate reference hold "aquisition time" and CDS output "settling time" needed for a particular application. Each of the selections listed in Table 3. have been optimized to provide only enough analog bandwidth to acquire a full scale input step, to 14-bit accuracy, in a single conversion. Increasing the analog bandwidth (using a faster settling and acquisition time) would only serve to potentially increase the amount of noise at the ADCDS-1403's output. The ADCDS-1403 uses a two bit digital word to select four different analog bandwidths for the ADCDS-1403's input stage (See Table 3. for details).

| INPUT AMPLIFIER VOUT, ① (VOLTS P-P) |           | SCALE             | DIGITAL OUTPUT    | OUT-OF-RANGE |

|-------------------------------------|-----------|-------------------|-------------------|--------------|

| Video Signal-Reference Signal       | >-2.80000 | >Full Scale –1LSB | 11 1111 1111 1111 | 1            |

|                                     | -2.80000  | Full Scale –1LSB  | 11 1111 1111 1111 | 0            |

|                                     | -2.10000  | 3/4FS             | 11 0000 0000 0000 | 0            |

|                                     | -1.40000  | 1/2FS             | 10 0000 0000 0000 | 0            |

| -0.70000                            |           | 1/4FS             | 01 0000 0000 0000 | 0            |

|                                     | -0.35000  | 1/8FS             | 00 1000 0000 0000 | 0            |

|                                     | -0.000171 | 1 LSB             | 00 0000 0000 0001 | 0            |

|                                     | 0         | 0                 | 00 0000 0000 0000 | 0            |

| Video Signal-Reference Signal       | <0②       | <0                | 00 0000 0000 0000 | 1            |

#### Table 2. Output Coding

Notes:

① Input Amplifier Vout = (Video Signal - Reference Level)

O The video portion of the differential signal (input-amplifier's Vour) must be more negative than its associated reference

level and Vout should not exceed  $\pm 2.8$ V DC.

#### <u>muRata</u> Ps Murata Power Solutions 14-Bit, 3 Megapixels/Second Imaging Signal Processor

# **ADCDS-1403**

| Table 3. Programmable Analog Bandwidth |                               |                |                |                                       |         |

|----------------------------------------|-------------------------------|----------------|----------------|---------------------------------------|---------|

| REFERENCE HOLD<br>"ACQUISITION TIME"   | CDS OUTPUT<br>"SETTLING TIME" | A0<br>(PIN 30) | A1<br>(PIN 31) | ADCDS-1403 MAXIMUM<br>CONVERSION RATE | –3DB BW |

| 100ns                                  | 120ns                         | 0              | 0              | 3MHz                                  | 10.5MHz |

| 200ns                                  | 250ns                         | 1              | 0              | 2MHz                                  | 6.6MHz  |

| 450ns                                  | 500ns                         | 0              | 1              | 1MHz                                  | 3.7MHz  |

| 600ns                                  | 1000ns                        | 1              | 1              | 0.5MHz                                | 2.5MHz  |

Note: See Figure 11. for timing details

#### Timing

The ADCDS-1403 requires two independently operated signals to accurately digitize the analog output signal from the CCD array.

- Reference Hold (pin 26) .

- Start Convert (pin 25)

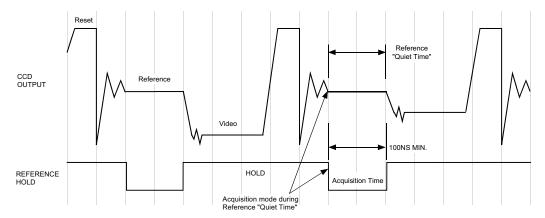

The "Reference Hold" signal controls the operation of an internal sample-hold circuit. A logic "1" places the sample-hold into the hold mode, capturing the value of the CCD's reference signal. The Reference Hold Signal allows the user to control the exact moment when the sample-hold is placed into the "hold" mode. For optimal performance the sample-hold

should be placed into the "hold" mode once the reference signal has fully settled from all switching transients to the desired accuracy (user defined).

Once the reference signal has been "held" and the video portion of the CCD's analog output signal appears at the ADCDS-1403's input, the ADCDS-1403's correlated double sampler produces a "CDS Output" signal (see Figure 11.) which is the difference between the "held" reference level and its associated video level. When the "CDS Output" signal has settled to the desired accuracy (user defined), the A/D conversion process can be initiated with the rising edge of a single start convert (Pin 25) signal.

www.murata-ps.com

# **ADCDS-1403**

Once the A/D conversion has been initiated, Reference Hold (Pin 26) can be placed back into the "Acquisition" mode in order to begin aquiring the next reference level. For optimal performance the ADCDS-1403's internal sample-hold should be placed back into the "Aquisition" mode (Reference Hold to logic "0") during the CCD's "Reference Quiet Time" ("Reference Quiet Time" is defined as the period when the CCD's reference

#### 14-Bit, 3 Megapixels/Second Imaging Signal Processor

signal has settled from all switching transients to the desired accuracy (see Figure 10.)). Placing the sample-hold back into the "aquisition" mode during the "Reference Quiet Time" prevents the ADCDS-1403's internal amplifiers from unecessarily tracking (reproducing) the large switching transients that occur during the CCD's reset to reference transition.

Note: For optimal performance (Fastest Acquisition Time), the ADCDS-1403 should be placed into the Acquisition mode (Reference Hold to logic "0") during the CCD output's Reference "Quiet Time". Reference "Quiet Time" is defined as the period when the reference signal's switching transients have settled to an acceptable (user defined) accuracy.

#### Figure 10. Reference Hold Timing

Note: As described in Figure 10, the 60ns min. is dependant on the quality of the CCD's Reference when the ADCDS-1403 is switched back into the track mode

Figure 11. ADCDS-1403 Timing Diagram

**ADCDS-1403**

14-Bit, 3 Megapixels/Second Imaging Signal Processor

#### **ORDERING INFORMATION**

| MODEL        | OPERATING<br>TEMPERATURE RANGE | 40-PIN<br>PACKAGE |

|--------------|--------------------------------|-------------------|

| ADCDS-1403   | 0 to 70°C                      | TDIP              |

| ADCDS-1403EX | –55 to 125°C                   | TDIP              |

### muRata Ps Murata Power Solutions

Murata Power Solutions, Inc.

11 Cabot Boulevard, Mansfield, MA 02048-1151 U.S.A.

Tel: (508) 339-3000 (800) 233-2765 Fax: (508) 339-6356

www.murata-ps.com email:sales@murata-ps.com ISO 9001 and 14001 REGISTERED 03/23/09

Murata Power Solutions, Inc. makes no representation that the use of its products in the circuits described herein, or the use of other technical information contained herein, will not infringe upon existing or future patent rights. The descriptions contained herein do not imply the granting of licenses to make, use, or sell equipment constructed in accordance therewith. Specifications are subject to change without notice.

| Mansfield (MA), Tel: (508) 339-3000, email: sales@murata-ps.com                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------|

| Toronto, Tel: (866) 740-1232, email: toronto@murata-ps.com                                                                         |

| Milton Keynes, Tel: +44 (0)1908 615232, email: mk@murata-ps.com                                                                    |

| Montigny Le Bretonneux, Tel: +33 (0)1 34 60 01 01, email: france@murata-ps.com                                                     |

| München, Tel: +49 (0)89-544334-0, email: munich@murata-ps.com                                                                      |

| Tokyo, Tel: 3-3779-1031, email: sales_tokyo@murata-ps.com<br>Osaka, Tel: 6-6354-2025, email: sales_osaka@murata-ps.com             |

| Shanghai, Tel: +86 215 027 3678, email: shanghai@murata-ps.com<br>Guangzhou, Tel: +86 208 221 8066, email: guangzhou@murata-ps.com |

| Parkway Centre, Tel: +65 6348 9096, email: singapore@murata-ps.com                                                                 |

|                                                                                                                                    |

www.murata-ps.com

Technical enquiries email: sales@murata-ps.com, tel: +1 508 339 3000