January 1993 Revised August 2000

# SCAN182541A Non-Inverting Line Driver with 25 $\Omega$ Series Resistor Outputs

### **General Description**

The SCAN182541A is a high performance BiCMOS line driver featuring separate data inputs organized into dual 9-bit bytes with byte-oriented paired output enable control signals. This device is compliant with IEEE 1149.1 Standard Test Access Port and Boundary-Scan architecture with the incorporation of the defined Boundary-Scan test logic and test access port consisting of Test Data Input (TDI), Test Data Out (TDO), Test Mode Select (TMS), and Test Clock (TCK).

### **Features**

- IEEE 1149.1 (JTAG) Compliant

- High performance BiCMOS technology

- $\blacksquare$  25 $\Omega$  series resistor outputs eliminate need for external terminating resistors

- Dual output enable signals per byte

- 3-STATE outputs for bus-oriented applications

- 25 mil pitch SSOP (Shrink Small Outline Package)

- Includes CLAMP, IDCODE and HIGHZ instructions

- Additional instructions SAMPLE-IN, SAMPLE-OUT and EXTEST-OUT

- Power up 3-STATE for hot insert

- Member of Fairchild's SCAN Products

### **Ordering Code:**

| Order Number   | Package<br>Number | Package Description                                                   |

|----------------|-------------------|-----------------------------------------------------------------------|

| SCAN182541ASSC | MS56A             | 56-Lead Shrink Small Outline Package (SSOP), JEDEC MO-118, 0.300 Wide |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

### **Connection Diagram**

|                   |    | · /    |    | 1                 |

|-------------------|----|--------|----|-------------------|

| TMS -             | 1  | $\cup$ | 56 | — TDI             |

| AO <sub>0</sub> - | 2  |        | 55 | — AI <sub>0</sub> |

| AOE <sub>1</sub>  | 3  |        | 54 | —Ā0Ē₂             |

| A0,-              | 4  |        | 53 | — AI <sub>1</sub> |

| A02 -             | 5  |        | 52 | — AI <sub>2</sub> |

| GND —             | 6  |        | 51 | — GND             |

| A03 -             | 7  |        | 50 | — Al3             |

| A04 -             | 8  |        | 49 | - AI4             |

| v <sub>cc</sub> — | 9  |        | 48 | −v <sub>cc</sub>  |

| A05-              | 10 |        | 47 | — AI5             |

| A0 <sub>6</sub> - | 11 |        | 46 | — AI6             |

| GND —             | 12 |        | 45 | — GND             |

| A07 -             | 13 |        | 44 | — Al <sub>7</sub> |

| A08 -             | 14 |        | 43 | — AI8             |

| BO <sub>0</sub> — | 15 |        | 42 | —вI <sub>0</sub>  |

| во, —             | 16 |        | 41 | —ві <sub>1</sub>  |

| GND -             | 17 |        | 40 | — GND             |

| BO <sub>2</sub> — | 18 |        | 39 | — ві <sub>2</sub> |

| во <sub>3</sub> — | 19 |        | 38 | —ві <sub>з</sub>  |

| v <sub>cc</sub> — | 20 |        | 37 | -v <sub>cc</sub>  |

| BO <sub>4</sub> — | 21 |        | 36 | —BI₄              |

| BO <sub>5</sub> — | 22 |        | 35 | —ві <sub>5</sub>  |

| GND -             | 23 |        | 34 | — GND             |

| во <sub>6</sub> — | 24 |        | 33 | — ві <sub>6</sub> |

| BO <sub>7</sub> — | 25 |        | 32 | —ві <sub>7</sub>  |

| BOE <sub>1</sub>  | 26 |        | 31 | —BOE <sub>2</sub> |

| во <sub>в</sub> — | 27 |        | 30 | —ві <sub>8</sub>  |

| TDO —             | 28 |        | 29 | — тск             |

|                   |    |        |    |                   |

#### Pin Descriptions

| Pin<br>Names                           | Description                              |

|----------------------------------------|------------------------------------------|

| AI <sub>(0-8)</sub>                    | Input Pins, A Side                       |

| BI <sub>(0-8)</sub>                    | Input Pins, B Side                       |

| AOE <sub>1</sub> ,                     | 3-STATE Output Enable Input Pins, A Side |

| BOE <sub>1</sub> ,<br>BOE <sub>2</sub> | 3-STATE Output Enable Input Pins, B Side |

| AO <sub>(0-8)</sub>                    | Output Pins, A Side                      |

| BO <sub>(0-8)</sub>                    | Output Pins, B Side                      |

# **Truth Tables**

|       | 40    |                     |                     |

|-------|-------|---------------------|---------------------|

| †AOE₁ | †AOE₂ | AI <sub>(0-8)</sub> | AO <sub>(0-8)</sub> |

| L     | L     | Н                   | Н                   |

| Н     | X     | X                   | Z                   |

| X     | Н     | X                   | Z                   |

| L     | L     | L                   | L                   |

|                    |       |  | i L     |

|--------------------|-------|--|---------|

| H = HIGH Voltage L | _evel |  | Z = Hi  |

| L = LOW Voltage Le | evel  |  | † = Ina |

L Z = High Impedance

†BOE<sub>1</sub>

L

Н

Χ

Inputs

†BOE<sub>2</sub>

L

Χ

Н

ı

BI<sub>(0-8)</sub>

Н

Χ

Χ

L

BO<sub>(0-8)</sub>

Н

Ζ

Ζ

L

# **Block Diagrams**

X = Immaterial

$<sup>\</sup>dagger = \mbox{Inactive-to-active transition}$  must occur to enable outputs upon power-up.

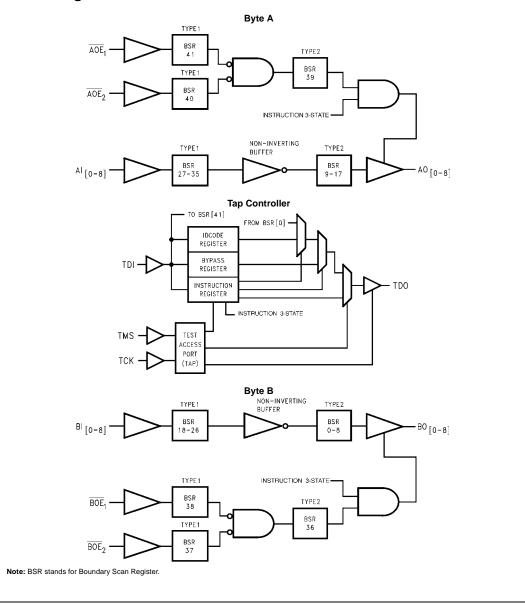

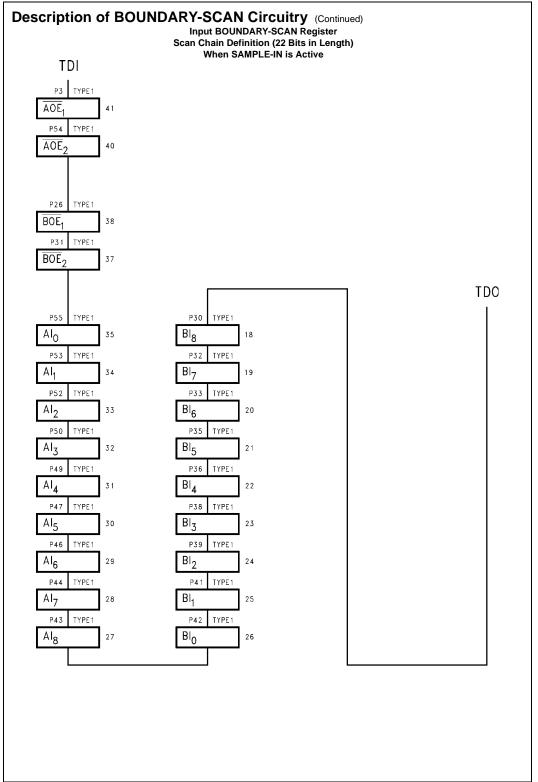

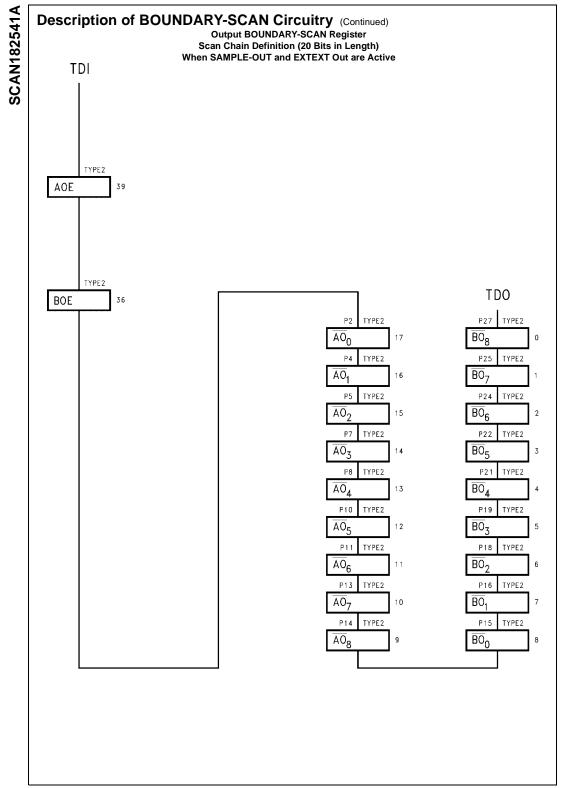

### **Description of BOUNDARY-SCAN Circuitry**

The scan cells used in the BOUNDARY-SCAN register are one of the following two types depending upon their location. Scan cell TYPE1 is intended to solely observe system data, while TYPE2 has the additional ability to control system data.

Scan cell TYPE1 is located on each system input pin while scan cell TYPE2 is located at each system output pin as well as at each of the two internal active-high output enable signals. AOE controls the activity of the A-outputs while BOE controls the activity of the B-outputs. Each will activate their respective outputs by loading a logic high.

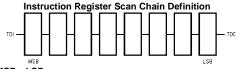

The BYPASS register is a single bit shift register stage identical to scan cell TYPE1. It captures a fixed logic low.

**Bypass Register Scan Chain Definition**

SCAN182541A Product IDCODE (32-Bit Code per IEEE 1149.1)

| Version | Entity | Part      | Manufacture<br>r | Required b<br>y |

|---------|--------|-----------|------------------|-----------------|

|         |        | Number    | ID               | 1149.1          |

| 0000    | 111111 | 000000100 | 00000001111      | 1               |

| MSB     |        |           |                  | LSB             |

The INSTRUCTION register is an 8-bit register which captures the default value of 10000001 (SAMPLE/PRELOAD) during the CAPTURE-IR instruction command. The benefit of capturing SAMPLE/PRELOAD as the default instruction during CAPTURE-IR is that the user is no longer required to shift in the 8-bit instruction for SAMPLE/PRELOAD. The sequence of: CAPTURE-IR→EXIT1-IR→ UPDATE-IR will update the SAMPLE/PRELOAD instruction. For more information refer to the section on instruction definitions.

$MSB \rightarrow LSB$

| Instruction Code | Instruction    |

|------------------|----------------|

| 00000000         | EXTEST         |

| 10000001         | SAMPLE/PRELOAD |

| 10000010         | CLAMP          |

| 00000011         | HIGH-Z         |

| 01000001         | SAMPLE-IN      |

| 01000010         | SAMPLE-OUT     |

| 00100010         | EXTEST-OUT     |

| 10101010         | IDCODE         |

| 11111111         | BYPASS         |

| All Others       | BYPASS         |

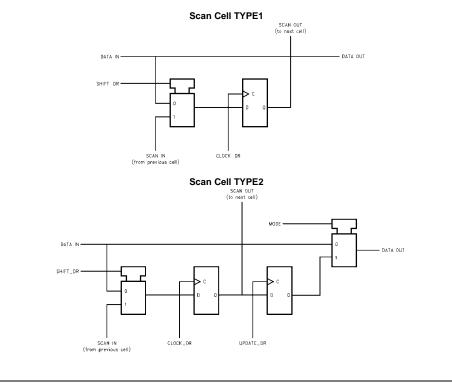

# Description of BOUNDARY-SCAN Circuitry (Continued) BOUNDARY-SCAN Register Definition Index

| Bit No. | Pin Name         | Pin No. | Pin Type | Scan Cell Type |         |

|---------|------------------|---------|----------|----------------|---------|

| 41      | AOE <sub>1</sub> | 3       | Input    | TYPE1          |         |

| 40      | AOE <sub>2</sub> | 54      | Input    | TYPE1          |         |

| 39      | AOE              |         | Internal | TYPE2          | Control |

| 38      | BOE <sub>1</sub> | 26      | Input    | TYPE1          | Signals |

| 37      | BOE <sub>2</sub> | 31      | Input    | TYPE1          |         |

| 36      | BOE              |         | Internal | TYPE2          |         |

| 35      | AI <sub>0</sub>  | 55      | Input    | TYPE1          |         |

| 34      | AI <sub>1</sub>  | 53      | Input    | TYPE1          |         |

| 33      | Al <sub>2</sub>  | 52      | Input    | TYPE1          |         |

| 32      | Al <sub>3</sub>  | 50      | Input    | TYPE1          |         |

| 31      | Al <sub>4</sub>  | 49      | Input    | TYPE1          | A–in    |

| 30      | Al <sub>5</sub>  | 47      | Input    | TYPE1          |         |

| 29      | AI <sub>6</sub>  | 46      | Input    | TYPE1          |         |

| 28      | Al <sub>7</sub>  | 44      | Input    | TYPE1          |         |

| 27      | Al <sub>8</sub>  | 43      | Input    | TYPE1          |         |

| 26      | BI <sub>0</sub>  | 42      | Input    | TYPE1          |         |

| 25      | BI <sub>1</sub>  | 41      | Input    | TYPE1          |         |

| 24      | BI <sub>2</sub>  | 39      | Input    | TYPE1          |         |

| 23      | BI <sub>3</sub>  | 38      | Input    | TYPE1          |         |

| 22      | BI <sub>4</sub>  | 36      | Input    | TYPE1          | B–in    |

| 21      | BI <sub>5</sub>  | 35      | Input    | TYPE1          |         |

| 20      | BI <sub>6</sub>  | 33      | Input    | TYPE1          |         |

| 19      | BI <sub>7</sub>  | 32      | Input    | TYPE1          |         |

| 18      | BI <sub>8</sub>  | 30      | Input    | TYPE1          |         |

| 17      | AO <sub>0</sub>  | 2       | Output   | TYPE2          |         |

| 16      | AO <sub>1</sub>  | 4       | Output   | TYPE2          |         |

| 15      | AO <sub>2</sub>  | 5       | Output   | TYPE2          |         |

| 14      | AO <sub>3</sub>  | 7       | Output   | TYPE2          |         |

| 13      | AO <sub>4</sub>  | 8       | Output   | TYPE2          | A-out   |

| 12      | AO <sub>5</sub>  | 10      | Output   | TYPE2          |         |

| 11      | AO <sub>6</sub>  | 11      | Output   | TYPE2          |         |

| 10      | AO <sub>7</sub>  | 13      | Output   | TYPE2          |         |

| 9       | AO <sub>8</sub>  | 14      | Output   | TYPE2          |         |

| 8       | BO <sub>0</sub>  | 15      | Output   | TYPE2          |         |

| 7       | BO <sub>1</sub>  | 16      | Output   | TYPE2          |         |

| 6       | BO <sub>2</sub>  | 18      | Output   | TYPE2          |         |

| 5       | BO <sub>3</sub>  | 19      | Output   | TYPE2          |         |

| 4       | BO <sub>4</sub>  | 21      | Output   | TYPE2          | B-out   |

| 3       | BO <sub>5</sub>  | 22      | Output   | TYPE2          |         |

| 2       | BO <sub>6</sub>  | 24      | Output   | TYPE2          |         |

| 1       | BO <sub>7</sub>  | 25      | Output   | TYPE2          |         |

| 0       | BO <sub>8</sub>  | 27      | Output   | TYPE2          |         |

### **Absolute Maximum Ratings**(Note 1)

Voltage Applied to Any Output

% in Disabled or Power-Off State  $$-0.5$\rm V to +5.5$\rm V_{CC}$$  in the HIGH State  $$-0.5$\rm V to V_{CC}$$

Current Applied to Output

DC Latchup Source Current -500 mA

Over Voltage Latchup (I/O) 10V

EDS (HBM) Min. 2000V

# Recommended Operating Conditions

**Note 1:** Absolute Maximum Ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

### **DC Electrical Characteristics**

| Symbol                             | Paramete                     | er               | $v_{cc}$ | Min  | Тур | Max  | Units | Conditions                         |

|------------------------------------|------------------------------|------------------|----------|------|-----|------|-------|------------------------------------|

| V <sub>IH</sub>                    | Input HIGH Voltage           |                  |          | 2.0  |     |      | V     | Recognized HIGH Signal             |

| V <sub>IL</sub>                    | Input LOW Voltage            |                  |          |      |     | 0.8  | V     | Recognized LOW Signal              |

| V <sub>CD</sub>                    | Input Clamp Diode Voltage    | ge               | Min      |      |     | -1.2 | V     | I <sub>IN</sub> = -18 mA           |

| V <sub>OH</sub>                    | Output HIGH Voltage          |                  | Min      | 2.5  |     |      | V     | $I_{OH} = -3 \text{ mA}$           |

|                                    |                              | •                | Min      | 2.0  |     |      | V     | I <sub>OH</sub> = -32 mA           |

| V <sub>OL</sub>                    | Output LOW Voltage           |                  | Min      |      |     | 0.8  | V     | I <sub>OL</sub> = 15 mA            |

| I <sub>IH</sub>                    | Input HIGH Current           | All Oth          | Max      |      |     | 5    | μА    | V <sub>IN</sub> = 2.7V (Note 3)    |

|                                    |                              | All Others       | Max      |      |     | 5    | μА    | $V_{IN} = V_{CC}$                  |

|                                    |                              | TMS, TDI         | Max      |      |     | 5    | μА    | $V_{IN} = V_{CC}$                  |

| I <sub>BVI</sub>                   | Input HIGH Current Brea      | kdown Test       | Max      |      |     | 7    | μА    | V <sub>IN</sub> = 7.0V             |

| I <sub>BVIT</sub>                  | Input HIGH Current Brea      | kdown Test (I/O) | Max      |      |     | 100  | μА    | V <sub>IN</sub> = 5.5V             |

| I <sub>IL</sub>                    | Input LOW Current            | A II O II        | Max      |      |     | -5   | μА    | V <sub>IN</sub> = 0.5V (Note 3)    |

|                                    |                              | All Others       | Max      |      |     | -5   | μА    | V <sub>IN</sub> = 0.0V             |

|                                    |                              | TMS, TDI         | Max      |      |     | -385 | μА    | V <sub>IN</sub> = 0.0V             |

| V <sub>ID</sub>                    | Input Leakage Test           |                  | 0.0      | 4.75 |     |      | V     | $I_{ID} = 1.9 \mu A$               |

|                                    |                              |                  |          |      |     |      |       | All Other Pins Grounded            |

| I <sub>IH</sub> + I <sub>OZH</sub> | Output Leakage Current       |                  | Max      |      |     | 50   | μА    | V <sub>OUT</sub> = 2.7V            |

| I <sub>IL</sub> + L <sub>OZL</sub> | Output Leakage Current       |                  | Max      |      |     | -50  | μА    | V <sub>OUT</sub> = 0.5V            |

| I <sub>OZH</sub>                   | Output Leakage Current       |                  | Max      |      |     | 50   | μА    | V <sub>OUT</sub> = 2.7V            |

| I <sub>OZL</sub>                   | Output Leakage Current       |                  | Max      |      |     | -50  | μА    | V <sub>OUT</sub> = 0.5V            |

| I <sub>OS</sub>                    | Output Short-Circuit Current |                  | Max      | -100 |     | -275 | mA    | V <sub>OUT</sub> = 0.0V            |

| I <sub>CEX</sub>                   | Output HIGH Leakage Current  |                  | Max      |      |     | 50   | μА    | V <sub>OUT</sub> = V <sub>CC</sub> |

| I <sub>ZZ</sub>                    | Bus Drainage Test            |                  | 0.0      |      |     | 100  | μА    | V <sub>OUT</sub> = 5.5V            |

|                                    |                              |                  |          |      |     |      |       | All Others Grounded                |

# DC Electrical Characteristics (Continued)

| Symbol           | Paramo                            | eter             | $v_{cc}$ | Min | Тур | Max  | Units | Conditions                               |

|------------------|-----------------------------------|------------------|----------|-----|-----|------|-------|------------------------------------------|

| I <sub>CCH</sub> | Power Supply Current              |                  | Max      |     |     | 250  | μΑ    | $V_{OUT} = V_{CC}$ ; TDI, TMS = $V_{CC}$ |

|                  |                                   |                  | Max      |     |     | 1.0  | mA    | $V_{OUT} = V_{CC}$ ; TDI, TMS = GND      |

| I <sub>CCL</sub> | Power Supply Current              |                  | Max      |     |     | 65   | mA    | $V_{OUT} = LOW; TDI, TMS = V_{CC}$       |

|                  |                                   |                  | Max      |     |     | 65.8 | mA    | $V_{OUT} = LOW; TDI, TMS = GND$          |

| I <sub>CCZ</sub> | Power Supply Current              |                  | Max      |     |     | 250  | μΑ    | TDI, TMS = V <sub>CC</sub>               |

|                  |                                   |                  | Max      |     |     | 1.0  | mA    | TDI, TMS = GND                           |

| I <sub>CCT</sub> | Additional I <sub>CC</sub> /Input | All Other Inputs | Max      |     |     | 2.9  | mA    | $V_{IN} = V_{CC} - 2.1V$                 |

|                  |                                   | TDI, TMS Inputs  | Max      |     |     | 3    | mA    | $V_{\text{IN}} = V_{\text{CC}} - 2.1V$   |

| I <sub>CCD</sub> | Dynamic I <sub>CC</sub>           | No Load          | Max      |     |     | 0.2  | mA/   | Outputs Open                             |

|                  |                                   |                  |          |     |     |      | MHz   | One Bit Toggling, 50% Duty Cycle         |

Note 3: Guaranteed not tested.

# **AC Electrical Characteristics**

Normal Operation:

|                  |                                               | V <sub>CC</sub> | $T_A$                  | Units |      |    |

|------------------|-----------------------------------------------|-----------------|------------------------|-------|------|----|

| Symbol           | Parameter                                     | (V)             | C <sub>L</sub> = 50 pF |       |      |    |

|                  |                                               | (Note 4)        | Min                    | Тур   | Max  |    |

| t <sub>PLH</sub> | Propagation Delay                             | 5.0             | 1.0                    | 3.4   | 5.2  |    |

| t <sub>PHL</sub> | Data to Q                                     |                 | 1.9                    | 4.1   | 6.5  | ns |

| t <sub>PLZ</sub> | Disable Time                                  | 5.0             | 2.0                    | 5.2   | 8.7  |    |

| t <sub>PHZ</sub> |                                               |                 | 1.9                    | 5.6   | 9.2  | ns |

| t <sub>PZL</sub> | Enable Time                                   | 5.0             | 2.4                    | 6.1   | 9.6  |    |

| t <sub>PZH</sub> |                                               |                 | 1.6                    | 5.1   | 8.5  | ns |

| t <sub>PLH</sub> | Propagation Delay                             | 5.0             | 3.2                    | 6.0   | 9.4  |    |

| t <sub>PHL</sub> | TCK to TDO                                    |                 | 4.5                    | 7.6   | 11.3 | ns |

| t <sub>PLZ</sub> | Disable Time                                  | 5.0             | 2.5                    | 5.8   | 9.9  |    |

| t <sub>PHZ</sub> | TCK to TDO                                    |                 | 3.7                    | 7.4   | 11.8 | ns |

| t <sub>PZL</sub> | Enable Time                                   | 5.0             | 4.9                    | 8.6   | 12.9 |    |

| t <sub>PZH</sub> | TCK to TDO                                    |                 | 3.1                    | 6.7   | 10.7 | ns |

| t <sub>PLH</sub> | Propagation Delay                             |                 | 3.7                    | 6.7   | 10.3 |    |

| t <sub>PHL</sub> | TCK to Data Out during Update-DR State        | 5.0             | 4.9                    | 8.3   | 12.4 | ns |

| t <sub>PLH</sub> | Propagation Delay                             |                 | 4.2                    | 7.9   | 12.2 |    |

| t <sub>PHL</sub> | TCK to Data Out during Update-IR State        | 5.0             | 5.3                    | 9.2   | 13.8 | ns |

| t <sub>PLH</sub> | Propagation Delay                             |                 | 5.0                    | 9.4   | 14.6 |    |

| t <sub>PHL</sub> | TCK to Data Out during Test Logic Reset State | 5.0             | 6.2                    | 10.9  | 16.4 | ns |

| t <sub>PLZ</sub> | Disable Time                                  |                 | 3.7                    | 7.9   | 13.0 |    |

| t <sub>PHZ</sub> | TCK to Data Out during Update-DR State        | 5.0             | 4.3                    | 8.7   | 13.7 | ns |

| t <sub>PLZ</sub> | Disable Time                                  |                 | 3.7                    | 8.5   | 14.2 |    |

| $t_{PHZ}$        | TCK to Data Out during Update-IR State        | 5.0             | 4.3                    | 9.4   | 14.8 | ns |

| t <sub>PLZ</sub> | Disable Time                                  |                 | 4.7                    | 10.1  | 16.6 |    |

| t <sub>PHZ</sub> | TCK to Data Out during Test Logic Reset State | 5.0             | 5.5                    | 10.9  | 17.3 | ns |

| t <sub>PZL</sub> | Enable Time                                   |                 | 5.5                    | 9.8   | 14.7 |    |

| t <sub>PZH</sub> | TCK to Data Out during Update-DR State        | 5.0             | 4.0                    | 7.9   | 12.5 | ns |

| t <sub>PZL</sub> | Enable Time                                   |                 | 5.8                    | 10.9  | 16.5 |    |

| t <sub>PZH</sub> | TCK to Data Out during Update-IR State        | 5.0             | 4.3                    | 9.0   | 14.4 | ns |

| t <sub>PZL</sub> | Enable Time                                   |                 | 6.6                    | 12.5  | 19.1 |    |

| t <sub>PZH</sub> | TCK to Data Out during Test Logic Reset State | 5.0             | 4.9                    | 10.5  | 16.9 | ns |

# **AC Operating Requirements**

Scan Test Operation:

| Symbol           | Parameter                                                                         | V <sub>CC</sub><br>(V)<br>(Note 5) | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ $C_L = 50 \text{ pF}$ Guaranteed Minimum | Units |

|------------------|-----------------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------|-------|

| t <sub>S</sub>   | Setup Time Data to TCK (Note 6)                                                   | 5.0                                | 2.2                                                                                          | ns    |

| t <sub>H</sub>   | Hold Time Data to TCK (Note 6)                                                    | 5.0                                | 1.8                                                                                          | ns    |

| t <sub>S</sub>   | Setup Time, H or L  AOE <sub>n</sub> , BOE <sub>n</sub> to TCK (Note 7)           | 5.0                                | 3.7                                                                                          | ns    |

| t <sub>H</sub>   | Hold Time, H or L  TCK to $\overline{AOE}_n$ , $\overline{BOE}_n$ (Note 7)        | 5.0                                | 1.8                                                                                          | ns    |

| t <sub>S</sub>   | Setup Time, H or L Internal AOE <sub>n</sub> , BOE <sub>n</sub> , to TCK (Note 8) | 5.0                                | 2.7                                                                                          | ns    |

| t <sub>H</sub>   | Hold Time, H or L TCK to Internal AOE <sub>n</sub> , BOE <sub>n</sub> (Note 8)    | 5.0                                | 1.8                                                                                          | ns    |

| t <sub>S</sub>   | Setup Time, H or L<br>TMS to TCK                                                  | 5.0                                | 7.5                                                                                          | ns    |

| t <sub>H</sub>   | Hold Time, H or L<br>TCK to TMS                                                   | 5.0                                | 1.8                                                                                          | ns    |

| t <sub>S</sub>   | Setup Time, H or L TDI to TCK                                                     | 5.0                                | 5.0                                                                                          | ns    |

| t <sub>H</sub>   | Hold Time, H or L<br>TCK to TDI                                                   | 5.0                                | 2.0                                                                                          | ns    |

| t <sub>W</sub>   | Pulse Width TCK H                                                                 | 5.0                                | 10.0<br>10.8                                                                                 | ns    |

| f <sub>MAX</sub> | Maximum TCK Clock Frequency                                                       | 5.0                                | 50                                                                                           | MHz   |

| t <sub>PU</sub>  | Wait Time, Power Up to TCK                                                        | 5.0                                | 100                                                                                          | ns    |

| $t_{DN}$         | Power Down Delay                                                                  | 0.0                                | 100                                                                                          | ms    |

Note 5: Voltage Range  $5.0V \pm 0.5V$

Note 6: This delay represents the timing relationship between the data input and TCK at the associated scan cells numbered 0-8, 9-17, 18-26 and 27-35.

Note 7: Timing pertains to BSR 38 and 41 or BSR 37 and 40.

Note 8: This delay represents the timing relationship between AOE/BOE and TCK for scan cells 36 and 39 only.

Note: All Input Timing Delays involving TCK are measured from the rising edge of TCK.

# Capacitance

| Symbol           | Parameter                   | Тур  | Units | Conditions, T <sub>A</sub> = 25°C |

|------------------|-----------------------------|------|-------|-----------------------------------|

| C <sub>IN</sub>  | Input Capacitance           | 5.8  | pF    | V <sub>CC</sub> = 0.0V            |

| C <sub>OUT</sub> | Output Capacitance (Note 9) | 13.8 | pF    | V <sub>CC</sub> = 5.0V            |

Note 9: C<sub>OUT</sub> is measured at frequency f = 1 MHz, per MIL-STD-883B, Method 3012.

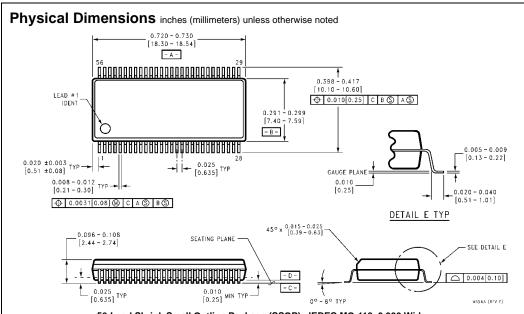

56-Lead Shrink Small Outline Package (SSOP), JEDEC MO-118, 0.300 Wide Package Number MS56A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com